US006314553B1

# (12) United States Patent

Stevens et al.

# (10) Patent No.: US 6,314,553 B1

(45) **Date of Patent:** Nov. 6, 2001

# (54) CIRCUIT SYNTHESIS AND VERIFICATION USING RELATIVE TIMING

(75) Inventors: **Kenneth S. Stevens**, Hillsboro, OR

(US); Shai Rotem, Hofit (IL); Ran Ginosar, Beaverton, OR (US)

(73) Assignee: Intel Corporation, Santa Clara, CA

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 09/184,417

(22) Filed: Nov. 2, 1998

(51) **Int. Cl.**<sup>7</sup> ...... **G06F 17/10**; G06F 7/60

(52) **U.S. Cl.** ...... **716/18**; 716/3; 716/1; 716/4; 716/6

### (56) References Cited

### U.S. PATENT DOCUMENTS

| 5,469,367 |   | 11/1995 | Puri et al 36               | 64/489 |

|-----------|---|---------|-----------------------------|--------|

| 5,748,487 |   | 5/1998  | Sawasaki et al 36           | 4/489  |

| 5,752,070 |   | 5/1998  | Martin et al 395/8          | 300.33 |

| 5,901,063 | * | 5/1999  | Chang et al                 | 716/4  |

| 5,930,148 | * | 7/1999  | Bjorksten et al             | 716/6  |

| 5,953,236 | * | 9/1999  | Hossain et al               | 716/6  |

| 5,956,497 | * | 9/1999  | Ratzel et al                | 716/1  |

| 6,009,252 | * | 12/1999 | Lipton                      | 716/5  |

|           |   |         | PT. PT. T. O. LOWE O. L. O. |        |

## OTHER PUBLICATIONS

Negulescu, R. et al, "Verification of speed-dependences in single-cell handshake circuits", 4th International Symposium on Advanced Research in Asynchronous Circuits & Systems, Apr. 1998.\*

Cortadella, J., et al., "Petrify: a tool for manipulating concurrent specifications and synthesis of asynchronous controllers", *IEICE Transactions on Information and Systems*, E80–D (3), pp. 315–325, (Mar. 1, 1997).

Stevens, K., et al., "CAD directions for high performance asynchronous circuits", *Proceedings of the Design Automation Conference*, New Orleans, LA, pp. 116–121, (Jun. 1999).

Stevens, K., et al., "Relative Timing", *Proceedings of the 5th International Symposium on Advanced Research in Asynchronous Circuits and Systems*, Barcelona, Spain, pp. 208–218, (Apr. 19–21, 1999).

Vanbekbergen, P., et al., "A design and validation system for asynchronous circuits", *Proceedings of the 32nd Design Automation Conference*, San Francisco, CA, pp. 725–730, (Jun. 12, 1995).

Chakraborty, S., et al., "Timing Analysis for Extended Burst-Mode Circuits", *IEEE Computer Soc.*, 101–111, (1997).

David, I., et al., "Self-Timed Architecture of a Reduced Instruction Set Computer", *Proceedings of the IFIP WG10.5 Working Conference on Asynchronous Design Methodologies*, A-28, Manchester, UK, 29-43, (Mar. 31-Apr. 2, 1993). Davis, A., et al., "Automatic Synthesis of Fast Compact Asynchronous Control Circuits", *Proceedings of the IFIP WG10.5 Working Conference on Asynchronous Design Methodologies*, A-28, Manchester, UK, 193-207, (Mar. 31,-Apr. 2, 1993).

(List continued on next page.)

Primary Examiner—Matthew Smith

Assistant Examiner—Jibreel Speight

(74) Attorney, Agent, or Firm—Schwegman, Lundberg, Woessner & Kluth, P.A.

## (57) ABSTRACT

A system and method of synthesizing and/or verifying a circuit from a behavioral description of that circuit. A signal ordering of signals in the circuit is defined, wherein defining a signal ordering of signals in the circuit includes specifying a relative ordering of a plurality of events within the circuit. The behavioral description is modified as a function of the signal ordering. The circuit is then synthesized and/or verified as a function of the modified behavioral description.

### 29 Claims, 27 Drawing Sheets

### OTHER PUBLICATIONS

Myers, C.J., Computer-Aided Synthesis and Verification of Gate-Level Timed Circuits (Asynchronous Circuits), A Dissertation submitted to the Department of Electrical Engineering and the Committee on Graduate Studies of Stanford University in Partial Fulfillment of the Requirements for the

Degree of Doctor of Philosophy, 1-127 p., (Oct. 1995).

Negulescu, R., et al., "Verification of Speed-Dependences in Single-Rail Handshake Circuits", *IEEE Computer Soc.*, 1–13 p., (Mar./Apr. 1998).

\* cited by examiner

Figure 5: Generalized C-Elements: (a) gC, (b) for  $\underline{a} \prec \underline{b}$ , gC=wire, (c) for  $\underline{a} \downarrow \prec \underline{b} \downarrow$  (d) for  $\underline{a} \uparrow \prec \underline{b} \uparrow$

| Hea HE | Fall                                                | Rise                                                                                                                          | Energy                                                                                                                                                                                       |                                                                                                                                                                                                                                                               | Test                                                                                                                                                                                                                                                                                                                  | Test                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                                     |                                                                                                                               |                                                                                                                                                                                              | Area                                                                                                                                                                                                                                                          | C-Elt                                                                                                                                                                                                                                                                                                                 | Spec RT2                                                                                                                                                                                                                                                                                                                                                                             |

|        | •                                                   | •                                                                                                                             | \ <u>-</u> /                                                                                                                                                                                 |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                       | 90%                                                                                                                                                                                                                                                                                                                                                                                  |

|        |                                                     |                                                                                                                               |                                                                                                                                                                                              |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                       | 92%                                                                                                                                                                                                                                                                                                                                                                                  |

| No     | 700                                                 | 545                                                                                                                           |                                                                                                                                                                                              |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                       | 100%                                                                                                                                                                                                                                                                                                                                                                                 |

| Yes    | 640                                                 | 585                                                                                                                           | 11.1                                                                                                                                                                                         | 10                                                                                                                                                                                                                                                            | 100%                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                      |

| Yes    | 735                                                 | 785                                                                                                                           | 14.0                                                                                                                                                                                         | 8                                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                                                                                     | 100%                                                                                                                                                                                                                                                                                                                                                                                 |

|        |                                                     | 600                                                                                                                           | 11.6                                                                                                                                                                                         | 9                                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                                                                                     | 100%                                                                                                                                                                                                                                                                                                                                                                                 |

|        | Has HF<br>circuit<br>Yes<br>No<br>Yes<br>Yes<br>Yes | circuit         delay           Yes         1170           No         700           Yes         640           Yes         735 | circuit         delay         delay           Yes         1170         1190           No         700         545           Yes         640         585           Yes         735         785 | circuit         delay         delay         (pJ)           Yes         1170         1190         20.2           No         700         545         11.6           Yes         640         585         11.1           Yes         735         785         14.0 | circuit         delay         delay         (pJ)         Area           Yes         1170         1190         20.2         16           No         700         545         11.6         18           Yes         640         585         11.1         10           Yes         735         785         14.0         8 | circuit         delay         delay         (pJ)         Area         C-Elt           Yes         1170         1190         20.2         16         100%           No         700         545         11.6         18         100%           Yes         640         585         11.1         10         100%           Yes         735         785         14.0         8         - |

Fig. 7: Comparison of C-Element implementations. Rise and fall times are in pS. Energy is per a complete cycle (rise and fall). Area is the number of transistors. Test columns show coverage using pseudo-stuck-at fault model on all inputs, outputs, and wire forks for the original specification and with RT3.

Fig. 7

Fig. %: Speed-Independent FIFO cell

Fig. 96

Figure **96**: Aggressive Relative Timed FIFO cell

Figure **?** Relative Timed Pulse-Mode FIFO

Figure 11: Relative Timed Burst-Mode FIFO implementation

Figure 12: Aggressive Relative Timed FIFO cell

Figure 13: Shuffled Aggressive Relative Timed FIFO cell

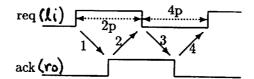

Figure 14: Four Cycle and Pulse Handshake Protocol Constraints

| Circuit | HF  | Worst<br>delay | Ave.<br>delay | рJ   | Area | $egin{array}{c} \mathbf{Test} \\ \mathbf{SI} \end{array}$ | $egin{array}{c} 	ext{Test} \ 	ext{RT13} \end{array}$ | Test<br>pulse |

|---------|-----|----------------|---------------|------|------|-----------------------------------------------------------|------------------------------------------------------|---------------|

| SI      | Yes | 2160           | 1560          | 37.6 | 39   | 98%                                                       | 91%                                                  | -             |

| RT-BM   | No  | 1020           | 550           | 32.2 | 40   | 95%                                                       | 74%                                                  | -             |

| RT-Agr  | No  | 595            | 390           | 18.2 | 20   | -                                                         | 100%                                                 | -             |

| Pulse   | No  | 350            | 350           | 16.2 | 17   | -                                                         | -                                                    | 100%          |

Fig. 15

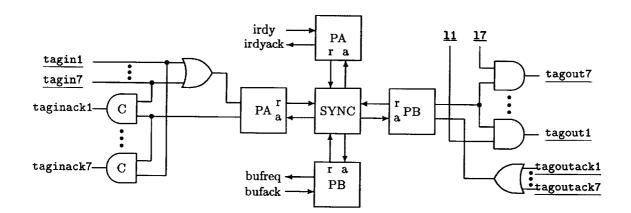

Speed-Independent Tag Unit. Assumes ti's are mutex.

Fig. 166

Figure 18 Illustration of timing assumptions on event ordering.

Figure 19; Simultaneity timing assumptions

Figure 20: Example to illustrate early enabling assumptions.

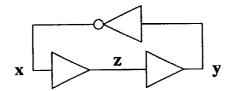

Figure  $\chi_{l}$ : The xyz example.

Figure 22: Example for automatic generation of timing assumptions.

Figure 23: Optimized circuit for the xyz example.

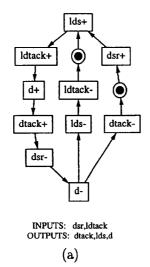

Figs. 24a+b

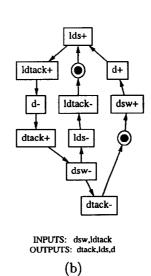

Figs. 25a+b

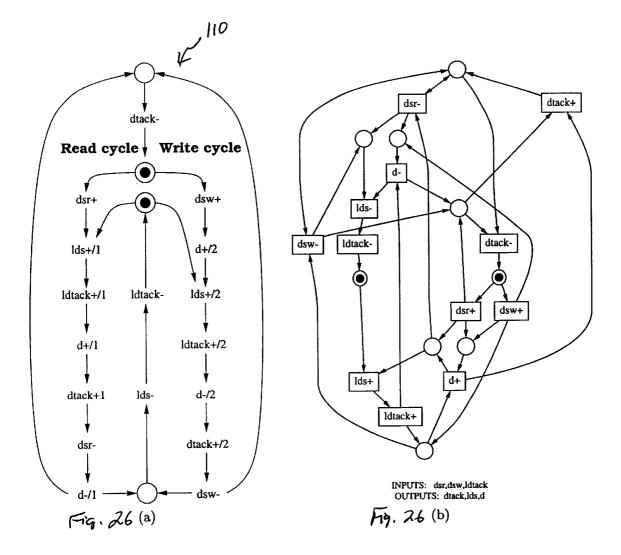

Fig. 27

Fig. 28a

Fig. 286

Fig. 29

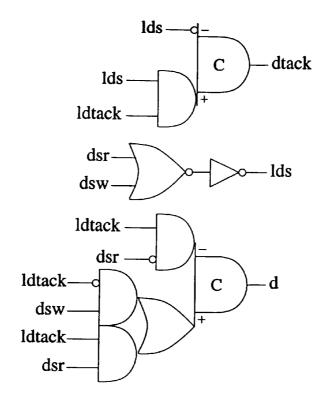

Figure 30: Circuit under the assumption of slow environment and lds- < | dtack-.

Figure 31 : Circuit under the assumption of a slow bus control logic.

Figure 33: Delay padding to satisfy timing assumptions.

# CIRCUIT SYNTHESIS AND VERIFICATION USING RELATIVE TIMING

### FIELD OF THE INVENTION

The present invention is related to integrated circuit fabrication, and more particularly to a system and method for synthesizing and verifying a timed circuit based on a behavioral description.

### **BACKGROUND INFORMATION**

The design of timing in digital circuits is an extremely difficult challenge. Conventional clocked digital design solves this problem by decomposing the circuit into cyclefree combinational logic (CL) stages and interstage clocked latches; the clock cycle is simply tuned to accommodate the worst-case propagation delay in the CL stages. The behavior of the combinational logic can then be specified and synthesized without considering timing. Speed Independent (SI) asynchronous circuits are analogous to clocked CL design 20 because SI circuits are independent of time—the behavior will be correct for any arbitrary gate delay.

High-performance circuits, both clocked and asynchronous, benefit from more aggressive timing methodologies. Clocked circuits can treat time locally to allow 25 adaptive and variable time in different parts of the circuit. Timed asynchronous and sequential circuits can have significantly enhanced performance, at the cost of lower robustness to delay variation.

Metric timing requires the specification of either propagation times or of ranges of propagation times. Unfortunately metric timing analysis can explode in complexity even when simple localized timing is used. The synthesis and verification of even moderate-sized timed circuits can therefore become intractable. Further, accurate metric ranges require layout parameters, which may not be present when a circuit is to be synthesized.

What is needed is a system and method of defining a circuit which frees the circuit from a dependence on propagation delays or on estimates of propagation delays while maintaining synthesis and verification of hazard-free designs.

### SUMMARY OF THE INVENTION

According to one aspect of the present invention, a system and method of performing logic synthesis from a behavioral description of a circuit is described. A signal ordering of signals in the circuit is defined, wherein defining a signal ordering of signals in the circuit includes specifying a relative ordering of a plurality of events within the circuit. The behavioral description is modified as a function of the signal ordering. The circuit is then synthesized as a function of the modified behavioral description.

According to another aspect of the present invention, a system and method of verifying a circuit from a behavioral description of that circuit is described. A signal ordering of signals in the circuit is defined, wherein defining a signal ordering of signals in the circuit includes specifying a relative ordering of a plurality of events within the circuit. The behavioral description is modified as a function of the signal ordering. The circuit is then verified as a function of the modified behavioral description.

According to yet another aspect of the present invention, a circuit includes a plurality of transistors and conductors 65 connecting two or more of the plurality of transistors. The conductors are defined and synthesized as a function of a

2

behavioral description of the circuit, wherein the behavioral description includes information specifying a relative ordering between a plurality of events within the circuit.

According to yet another aspect of the present invention, a computer readable medium includes program code for representing a circuit through a behavioral description of the circuit, program code for defining a signal ordering of signals in the circuit, wherein defining includes specifying a relative ordering of a plurality of events within the circuit, program code for modifying the behavioral description as a function of the signal ordering and program code for synthesizing the circuit as a function of the modified behavioral description.

According to yet another aspect of the present invention, a computer readable medium includes program code for representing a circuit through a behavioral description of the circuit, program code for defining a signal ordering of signals in the circuit, wherein defining includes specifying a relative ordering of a plurality of events within the circuit, program code for modifying the behavioral description as a function of the signal ordering and program code for verifying the circuit as a function of the modified behavioral description.

### BRIEF DESCRIPTION OF THE DRAWINGS

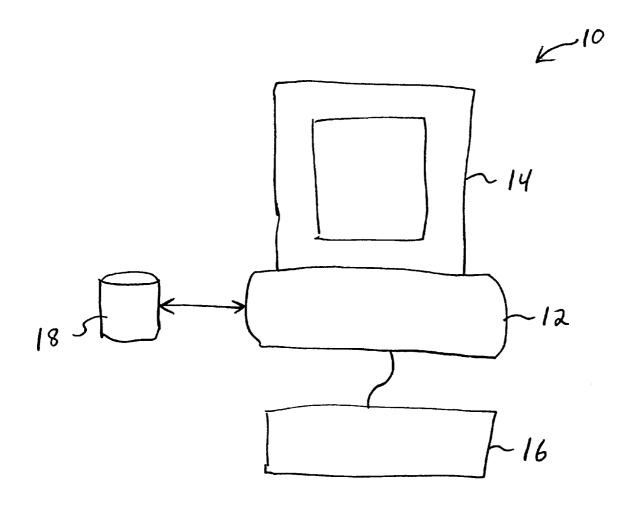

FIG. 1a illustrates a logic synthesis system according to the present invention;

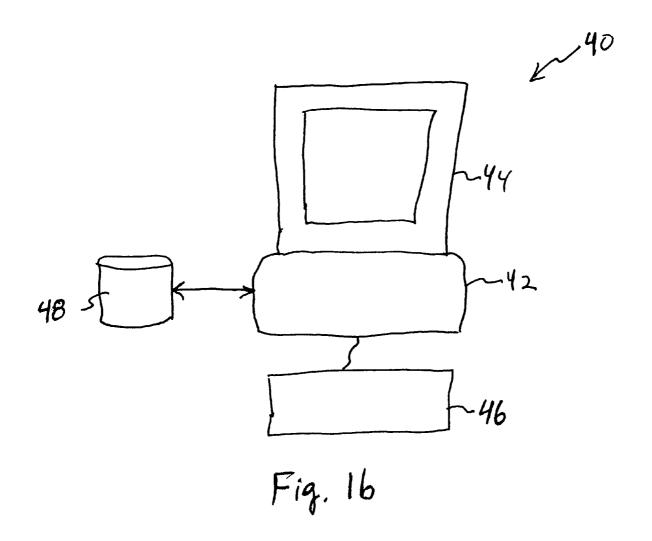

FIG. 1b illustrates a logic verification system according to the present invention;

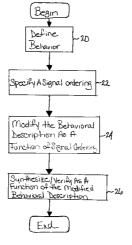

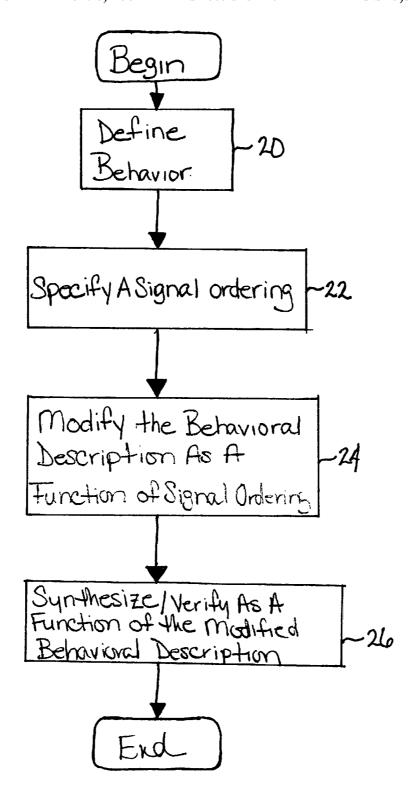

FIG. 2 illustrates a method of synthesizing and/or verifying logic according to the present invention;

FIG. 3 illustrates a computer readable medium storing program code applying the protocol of FIG. 2;

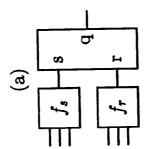

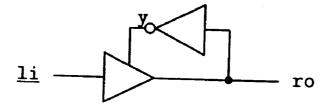

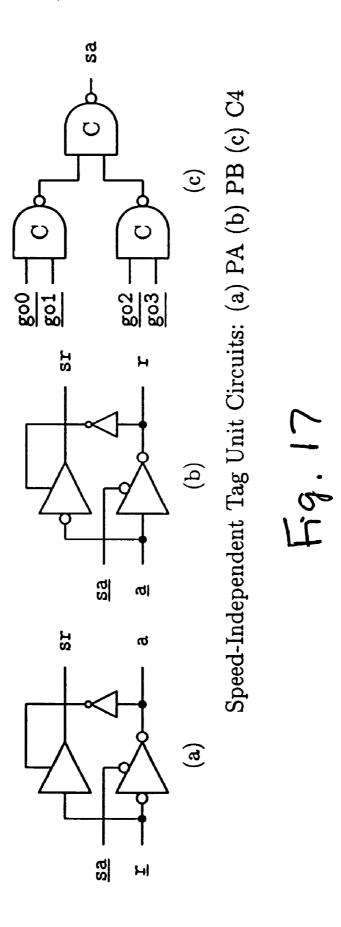

FIGS. 4*a*–*c* illustrate synthesis of a set-reset flop;

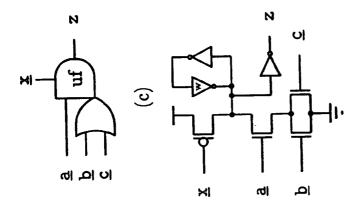

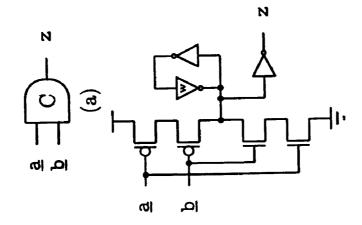

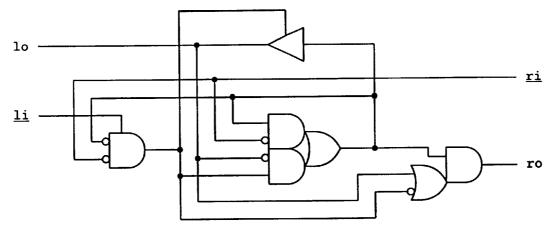

FIGS. 5a-d illustrate the evolution of a simple two-input generalized C-element through application of a series of relative timing assumptions according to the present invention:

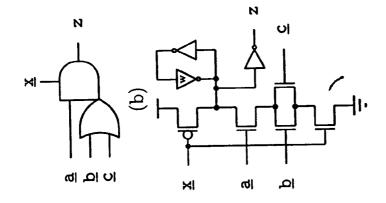

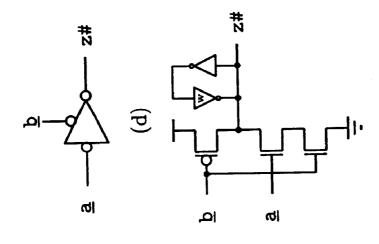

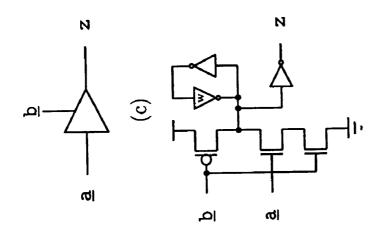

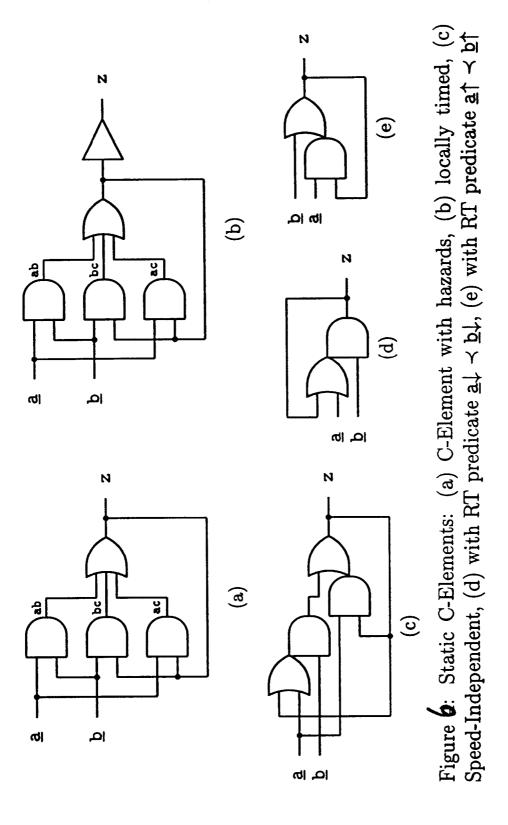

FIGS. 6*a*–*e* illustrate the evolution of a static AND-OR C-element through application of a series of relative timing assumptions according to the present invention;

FIG. 7 is a table comparing attributes of the circuits of FIGS. 6a-e;

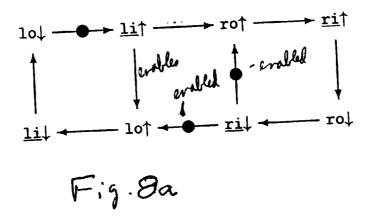

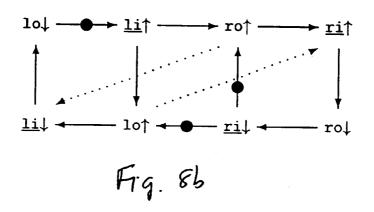

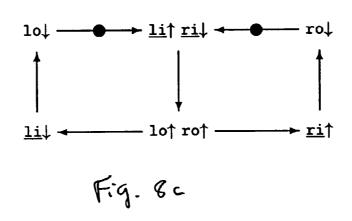

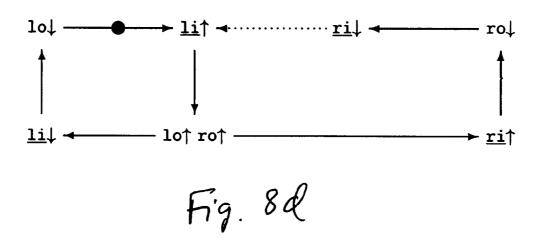

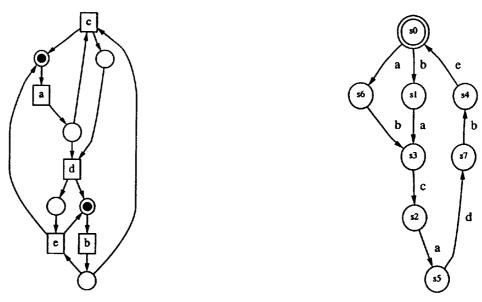

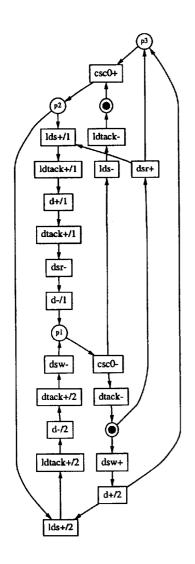

FIGS. **8***a*–*d* are Petri net illustrations of a FIFO simplified through the application of relative timing assumptions according to the present invention;

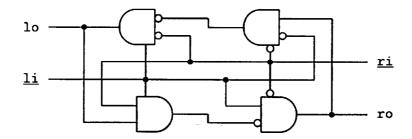

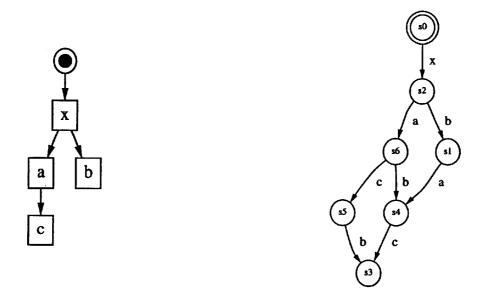

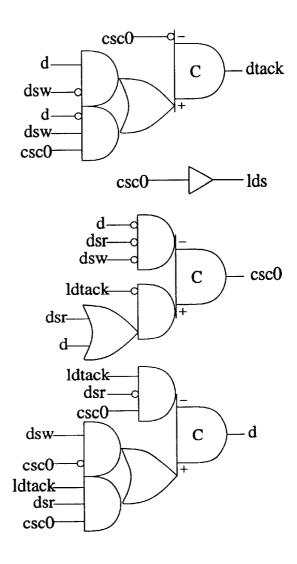

FIGS. 9a-d illustrate the evolution of a FIFO through application of a series of relative timing assumptions according to the present invention;

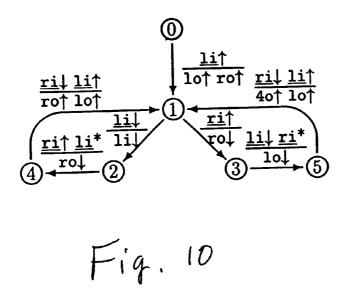

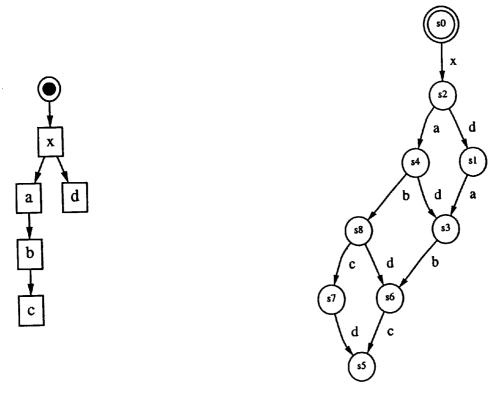

FIG. 10 illustrates a 3D state machine;

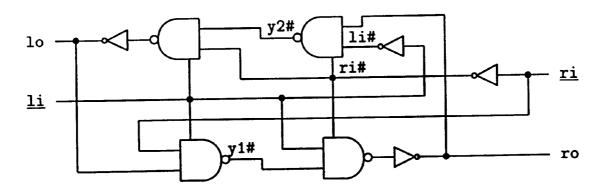

FIG. 11 illustrates a physical implementation of the circuit definition of FIG. 9b;

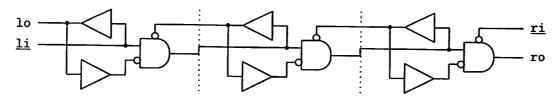

FIG. 12 illustrates a relative timed pulse-mode FIFO cell; FIG. 13 illustrates a shuffled version of the FIFO cell of FIG. 12;

FIG. 14 illustrates a four cycle request-acknowledge handshake:

FIG. 15 is a table comparing attributes of the circuits of FIGS. 9a-d;

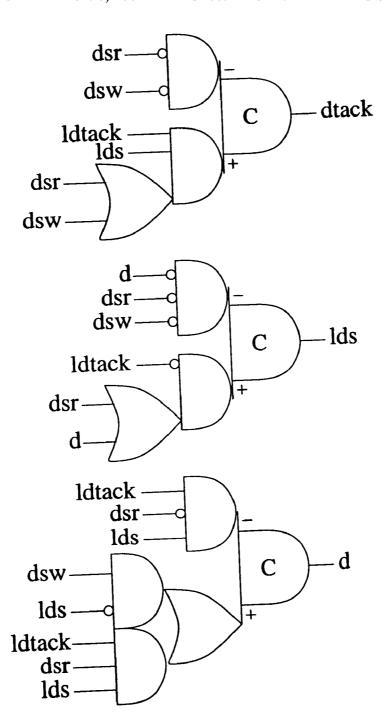

FIGS. **16***a* and *b* illustrate the evolution of a Tag Unit through application of a series of relative timing assumptions according to the present invention;

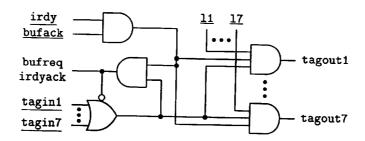

FIG. 17 illustrates various elements of the Tag Unit shown in FIG. 16a;

FIG. 18 is an illustration of timing assumptions on event ordering;

FIG. 19 is an illustration of simultaneity timing assumptions:

FIG. 20 is an illustration of early enabling assumptions;

FIG. 21 is an example of an xyz circuit;

FIG. 22 is an example of automatic generation of timing assumptions for the circuit of FIG. 21;

FIG. 23 is an optimized version of the circuit of FIG. 21 10 according to the present invention;

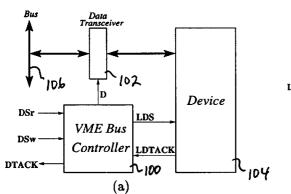

FIGS. 24a and b illustrate the I/O interface of a VME bus controller:

FIGS. 25a and b illustrate a state graph of the READ and WRITE cycle, respectively for the I/O interface of FIGS. 24a and b;

FIGS. **26***a* and *b* illustrate alternate versions of a state graph describing the complete behavior of the I/O interface of FIGS. **24***a* and *b*;

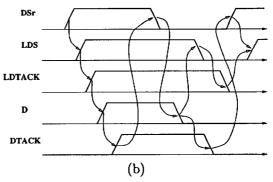

FIG. 27 illustrates the notation used to represent generalized C element;

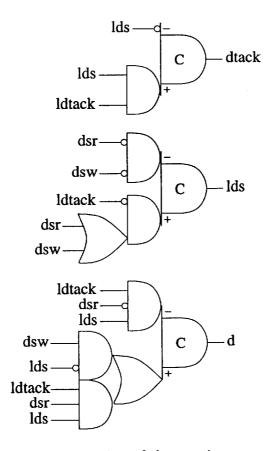

FIGS. 28a and 28b illustrate a specification of the VME bus controller of FIGS. 24a and b and one speed-independent embodiment of that specification;

FIG. 29 illustrates a relative-timed embodiment of the circuit of FIG. 28a assuming a slow environment; and

FIG. 30 illustrates an alternate relative-timed embodiment of the circuit of FIG. 28a assuming a slow environment; and

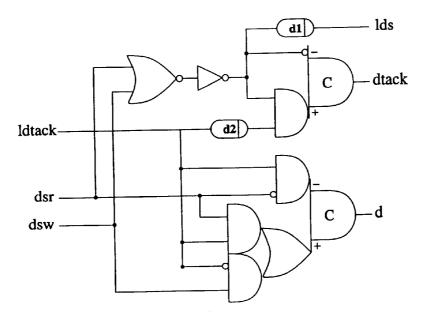

FIG. 31 illustrates a relative-timed embodiment of the circuit of FIG. 28a assuming a slow environment and slow bus control logic;

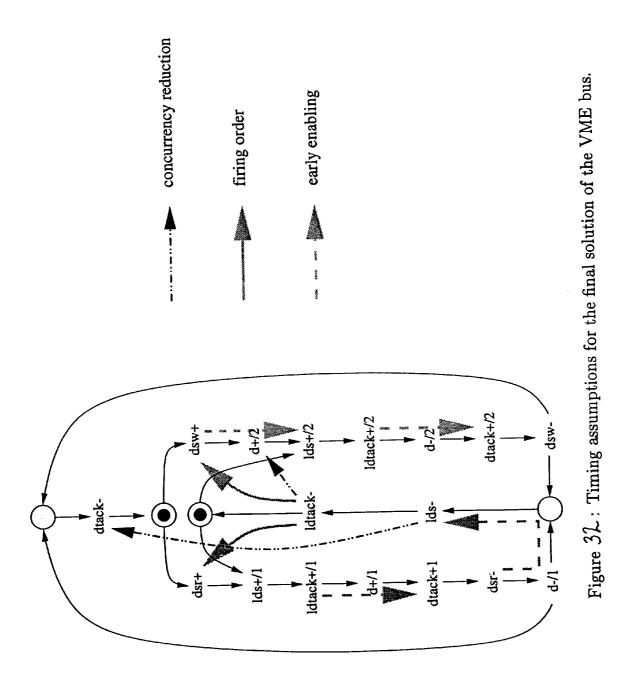

FIG. 32 illustrates a timing analysis of the circuit of FIG. 31; and

FIG. 33 illustrates delay padding within FIG. 31 in order to satisfy timing assumptions.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

In the following detailed description of the preferred embodiments, reference is made to the accompanying drawings which form a part hereof, and in which is shown by way of illustration specific embodiments in which the invention may be practiced. It is to be understood that other embodiments may be utilized and structural changes may be made without departing from the scope of the present invention.

A logic synthesis system 10 is shown in FIG. 1a. FIG. 1a illustrates a workstation having a processing unit 12 connected to a display 14 and a data entry device 16. Processing unit 12 includes a memory device 18 used to store program code according to the present invention.

Logic synthesis system 10 uses the behavioral description of a circuit to synthesize that circuit. In one embodiment, program code installed in the workstation, when executed, modifies the behavioral description as a function of the relative ordering of one or more signals in the circuit and synthesizes the circuit as a function of the modified behavioral description.

A logic verification system 40 is shown in FIG. 1b. FIG. 1b illustrates a workstation having a processing unit 42 connected to a display 44 and a data entry device 46. Processing unit 42 includes a memory device 48 used to store program code according to the present invention.

Logic verification system 40 uses the behavioral description of a circuit to verify operation of that circuit. In one

4

embodiment, program code installed in the workstation, when executed, modifies the behavioral description as a function of the relative ordering of one or more signals in the circuit and verifies the circuit as a function of the modified behavioral description.

Relative timing is a new method of representing and reasoning about delays in synchronous and asynchronous circuits. In one embodiment, the designer adds further definition to the behavioral description of a circuit by making assertions regarding relative ordering of events (e.g., signal A goes high before signal B goes low). Synthesis and verification algorithms use these assertions to constrain the large state space and improve on the quality of the synthesis, and to increase the capacity of the verification. In one embodiment, the relative timing constraints are expressed as a system of inequalities that can be proven to hold in any system by examining path delays.

As noted above, the synthesis of speed-independent circuits assumes a delay model that can be considered too conservative for the temporal behavior expected from the actual environment of the circuit and the technology used to implement it. Relative timing constraints, by making some timing assumptions on the behavior of the environment and the circuit itself, allow the designer to simplify the circuit being synthesized. Such a circuit may not, however, retain a crucial property of speed-independent circuits, i.e., the circuit may not react correctly for all possible delays of the components of the system. For this reason, it is crucial to know under which conditions the circuit behaves properly.

One example of an application of relative timing to a behavioral description is shown in FIG. 2. In FIG. 2, at 20 a circuit is described via a behavioral description. At 22, an ordering is defined between two or more signals within the circuit. This ordering is not defined, for instance, by defining when in time the signals change state. Instead, it is defined by a more amorphous relative timing relationship—one that is limited to stating "signal a occurs sometime before signal b". At 24 the behavioral description is modified as a function of the relative timing relationship defined for the signals and at 26 the circuit is synthesized or verified as a function of the modified behavioral description. In one embodiment, logic synthesis system 10 and logic verification system 40 generate relative timing assumptions automatically from the behavioral description. In one such embodiment logic verification system 40 identifies and verifies relative timing constraints in circuits that are not speed independent.

Program code applying these methodologies can be distributed using computer medium 30 as is shown in FIG. 3.

Relative timing can be used in both asynchronous and synchronous designs to reduce circuit complexity, power and area and increase the performance and testability of the design. For example, application of relative timing to a circuit used in a microprocessor design contributed significantly to a threefold improvement in performance and twofold reduction in power when compared to a similar circuit in a 400 MHz Pentium® processor, all for only a 15% increase in the area of the circuit. In addition, the new circuit had a 95% pseudo stuck-at testability.

Other benefits of applying a relative timing design approach include the ability to simplify the interface to a clocked design, verification support for burst-mode and complex gate synthesis engines, pulse-mode circuits, and hand-designed timed circuits. The numerous benefits and applications of relative timing will be described using design examples, as is detailed below.

In the following discussion, equations are employed to describe relationships between signals in a circuit. In the

50

5

discussion, input signals are identified by underlining the signal name, inverted signals are identified by placing a # after the signal name, a rising transition is identified by placing a  $\uparrow$  after the symbol name while a falling transition is identified by placing a  $\downarrow$  after the symbol name. A signal which is not underlined is an output signal. These conventions are illustrated in Table 1. For CCS, '.' is the sequential operator, '+' is the non-deterministic choice operator, '|' is parallel composition and '\{a}' is the restriction operator applied to a signal a.

| Signal                                                             | Description                         | Example                             |

|--------------------------------------------------------------------|-------------------------------------|-------------------------------------|

| input signal<br>output signal                                      | underline                           | <u>input</u><br>output              |

| inverted (asserted low)<br>rising transition<br>falling transition | hash mark<br>up arrow<br>down arrow | z# <sup>1</sup><br>a↑<br><u>b</u> ↓ |

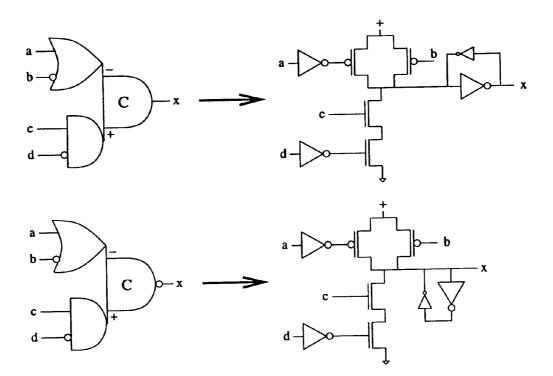

The following examples are based on non-clocked domino gates employing a single p device. Asynchronous tools such as 3D, ATACS and Petrify can typically synthesize set-reset flops and the appropriate functions (an example is shown in FIG. 4a). Technology mapping can then 25 be used to map the functions of FIG. 4a into single-variable reset (equivalently set) functions, and to implement them using standard footed domino gates as is shown in FIG. 4b. (FIG. 4b illustrates a footed domino gate (symbol and circuit) implementing a Set-Reset flop with  $\frac{1}{r} = x\#$ ,  $\frac{1}{r} = x \times 30$  a×(b+c).) When the reset variable is not used in the set function, an unfooted domino gate is used instead as is shown in FIG. 4c). (FIG. 4c illustrates an unfooted domino gate (symbol and circuit) implementing a Set-Reset flop with  $\frac{1}{r} = x\#$ ,  $\frac{1}{r} = x\#$

A simple two-input generalized C-Element C=(a|b).z.C (as defined in CCS) and its CMOS implementation are shown in FIG. 5a. Given the assumption that

RT1: a<b

the C-Element is reduced to a buffer: C=b.z.C. If the assumption is limited to the negative edges,

the reset function contains only  $b\downarrow$ , and the C-Element can be implemented as a footed domino gate (FIG. 5c):C=  $a\downarrow.b\downarrow.z\downarrow.(a\uparrow|b\uparrow).z\uparrow.C$ . With a similar assumption on the positive edges,

inverted inputs can be applied and the non-buffered z# output of the domino gate can be used. One such approach is shown in FIG. 5d. Alternatively, the output can be buffered for high loads. A "wobbly" C-Element C=a.b.z.C+b.(a.z.C+b.C), which is unsafe (allowing the input b to toggle and withdraw) can also be synthesized as above.

A static AND-OR C-Element is shown in FIG. 6a. This circuit is not speed-independent, but is safe provided the environment is sufficiently slow. If, for instance, the environment acts fast, b↓ may immediately follow z↑, before node ac has stabilized at '1'. The following requirements can be added to correct the situation:

RT4: bc↑<a↓

RT**5**: ac↑<b↓

6

RT1-5 are termed relative timing (RT) predicates. They define various timing assumptions to systems 10 and 40.

In one embodiment, RT4 and RT5 are generated by a verification tool. The verification tool identifies races in the system using its verification algorithms.

These specifications apply to inputs and intermediate variables, and thus the synthesized circuit should ensure these orderings based on environmental delays. These requirements are the same as burst-mode requirements; they guarantee the circuit is stable before new inputs arrive. The following is another set of predicates that are less restrictive because they do not require circuit stability:

RT6: bc↑<ab↓

RT7: ac↑<ab↓

One possible implementation that can guarantee these predicates hold is shown in FIG. 6b, where a buffer is added at the output. All constraints can be made local to the circuit if the buffer delay is large enough to guarantee that act  $\uparrow$  and bc $\uparrow$  precede  $z\uparrow$ . Alternatively, Petrify synthesizes the static complex gate circuit shown in FIG. 6c, which can be verified speed-independent.

Assumptions RT2 or RT3 lead to the simpler static circuits of FIGS. 6d and 6e, respectively. Note that these two circuits are actually subcircuits of the speed-independent

FIG. 7 summarizes the five alternative designs. The results are based on simulations made using standard library cell device sizes driving six standard inverters as a load. They were simulated in Spice using MOSIS 0.5 $\mu$  process parameters. Except for the static C-Element (SC), all implementations are hazard-free.

As can be seen in FIG. 7, the speed-independent circuit (SIC) is slower than all others, although the relative timing assumption (SIC-RT), which leads to a half size circuit, also enhances performance by 30%. The original static C requires the largest circuit but it is also relatively fast. The reduced domino C-Element (GC-RT) is 15% faster to rise (having only a single pull-up transistor), but is actually slower than the gC on the falling edge.

One approach of applying relative timing to the development of a circuit is to synthesize the circuit as a speed-independent design. The design is then simplified through careful application of relative timing assumptions. An example of such an approach is shown in FIGS. 9a-d, which illustrate the design of a simple FIFO cell.

A simple FIFO cell can be specified in CCS as follows:

$LEFT=li\uparrow.c.lo\uparrow.li\downarrow lo\downarrow.LEFT$

RIGHT=c.ro↑.ri↑.ro↓.ri↓.RIGHT

$$FIFO=(LEFT|RIGHT)\setminus \{c\} \tag{1}$$

where c is a label and c is a colabel.

Specification (1) consists of two handshake processes, LEFT and RIGHT. The c signal synchronizes the two processes so that ri must lower and li must raise before both processes may proceed. This process-based specification can easily be mapped to the equivalent petri-net of FIG. 8a. A speed-independent version of the FIFO can be synthesized using Petrify. The resulting circuit is shown in FIG. 9a.

This circuit definition uses the complex gate assumptions where the inverters are zero-delay or are combined with the complex gates. This definition, as well as a physical circuit implementation that includes discrete inverters, can be proven to conform to the specification of the FIFO in Specification (1) using a software package called Analyze.

The circuit of FIG. 9a pays a considerable delay penalty to achieve speed independence. Note, for instance, that lo↑ is produced after three complex gate delays, and ro↑ in four. Performance can be improved if one assumes that a circuit can be built that ensures that concurrent outputs are generated faster than they can be acknowledged by the environment. This assumption can be formulated as follows:

RT**8**: lo↑<ri↑

RT**9**: ro↑<li↓

A new specification is generated by adding these two relative timing predicates to the specification. The specification can be represented as:

$$FIFO\Lambda lo \uparrow \langle ri \uparrow \Lambda ro \uparrow \langle li \downarrow$$

(2)

where FIFO is the specification from Specification (1). This petri-net of FIG. 8b where the dashed arrows are relative timing constraints.

Note that the two relative timing constraints, RT8 and RT9, are in a form where outputs precede inputs. In addition, note from the specification that the outputs are enabled concurrently from a pair of inputs. This is exactly a burst-mode constraint where the input burst is  $\{\text{li}\uparrow\text{ri}\downarrow\}$  and the output burst is  $\{\text{lo}\uparrow\text{ro}\uparrow\}$ . The relative timing (RT) predicates constrain the environment so that both outputs are produced before either input is passed to the circuit. A Petri net showing this burst-mode behavior has been derived from the Petri net of FIG. 8b. It is shown in FIG. 8c. Incorporating the RT predicates RT8 and RT9 directly into Specification (1) produces the Mealy state machine of FIG. 10. This new form is suitable for synthesis through 3D and results in the symmetric circuit definition of FIG. 9b, which is hazard free with zero-delay inverters.

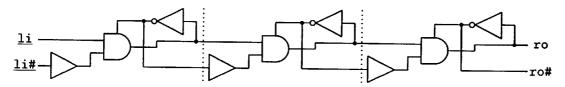

This symmetric circuit definition conforms to Specification (2), and achieves a considerable performance improvement over the speed-independent definition. Mapping the circuit definition of FIG. 9b to a physical implementation such as that shown in FIG. 11, however, reveals a problem. The circuit does not conform unless the inverters have zero delay. Unbounded delay in the inverters results in critical races which can cause the physical implementation to fail to conform to the specification. Fortunately, relative timing can be applied to the physical circuit to order these races in such a way that the circuit can conform to the specification. The following are the RT constraints that the circuit must meet in order to avoid the races.

RT10: y2#<<ii/>ri#

RT**12**: li#↓<ro↑

These constraints were generated by verification algorithms; they apply only to the physical implementation and 55 must be validated by a timing verifier to ensure that the races are not critical.

A further modification of the speed-independent circuit of FIG. 9a is possible. Assume that the circuit of Specification (2) can be placed in a large ring with a single token. If the 60 ring is sufficiently large, circuit delays will ensure that the token will always arrive at an idle cell. In a large ring, therefore, the handshake in the process RIGHT will always complete and the RIGHT interface will become idle before the LEFT interface becomes active.

The SI or BM circuit can safely be used in such an environment. If, however, one takes advantage of the timing

8

of the system a vastly improved circuit (in terms of power, performance, area and testability) can be synthesized. RT13 is the predicate for this environment:

RΤ**13**: ri↓<li↑

This assumption can be graphically represented as shown in FIG. 8d, where the dotted arc is the relative timing relation shown in RT13.

It should be noted that the dotted arc is not a causal arc; ri must lower before li can raise but ri cannot delay li. That is, the designer is assuming that there will always be a token on the dotted arc; the designer must, therefore, make sure that ri going low will always happen before lo going low.

This represents a major change in the operation of the circuit; the LEFT process is no longer synchronized directly with the RIGHT process. Instead the synchronization is through system timing.

The circuit in FIG. 9c can be synthesized with 3D from specification (2) with the RTpredicate RT13. Signal lo must be generated long enough after li so as to not disable the domino AND gate before it is fully set. This results in a number of RT constraints on critical races in the circuit. If, however, the timing of the lo signal can be correctly adjusted in the system to satisfy the RT constraints and to eliminate races, the result is the fast, small, testable circuit shown in FIG. 9c.

A pulse-mode FIFO cell can also be designed through the use of relative timing constraints applied to a program such as ATACS. As an alternate approach a pulse-mode circuit can be derived from RT13.

Through transitivity of the timing assumption shown in FIG. 8d, ro↓ must precede li↑, allowing us to remove the signal ri↑ altogether. This can be demonstrated by viewing part of the ring as is shown in FIG. 12.

Observe that the lo signal is nothing more than a delayed version of the li signal. Shuffling the lo devices and bubbles results in the circuit of FIG. 13, a circuit that has only forward-moving signals without any feedback. The shuffling that removes acknowledgment is directly based on RT13, which dissociated the LEFT process from the RIGHT. This shuffling removes output lo and input ri, making them local signals.

Note that signal li# in FIG. 13 is just li inverted. A transition li ↑ creates a short period when both li and li# are high, which will set the output of the domino gate. The duration of these signals being high depends on the delay in the li# path. This signal pair can be combined into a single wire li if the signal on this wire operates as a pulse. The final circuit derivation can be seen in FIG. 9d.

The specification for the pulse-mode circuit follows:

LEFTP=li↑. c.li↓.LEFT

RIGHTP=c:ro↑.ro↓: RIGHT

$PULSE=(LEFTP|RIGHTP)\setminus \{c\} \text{ ro} < \text{li} \uparrow$  (3)

Designing reliable pulse-mode circuits is very difficult. Some of the constraints of pulse circuits can be observed by understanding how the pulse-mode circuit was derived for this example. FIG. 14 shows a four cycle request-acknowledge handshake. Constraints 1 through 4 are causal with speed-independent signaling. By removing the acknowledgment signal (lo and ri in this case), we are left only with a request signal that requires constraints 2p and 4p. These constraints contain both minimum and maximum metric bounds. However, the actual requirements for the size of these bounds can be represented with relative timing arcs.

Interestingly, these arcs correspond to a protocol very similar to the standard request acknowledge handshaking. The pulse on li of FIG. 9d causes the output pulse ro, as required by specification (3). If we map req to li and ack to ro in FIG. 14, we see that arc 1 is causal.

This circuit can fail, however, if the pulse is so short that lo \( \( \ack \\ \) does not occur. This can be prevented by placing a relative timing transition that requires lo↑ (ack↑) before li  $\downarrow$  (req  $\downarrow$  ). This makes arc 2 in FIG. 14 an RT predicate, and slightly restricts the specification. (It may be possible to not 10 restrict the specifications behavior if an internal signal toggles which ensures the domino gate has changed state.)

The circuit will also fail if the li (req) pulse is too long. If ro  $\downarrow$  (ack  $\downarrow$ ) and  $y \uparrow$  have occurred before li  $\downarrow$  (req  $\downarrow$ ) then the circuit will fail. Therefore, arc 3 in FIG. 14 is a necessary 15 RT predicate for the circuit to work. Finally, arc 4 is assumed to hold given RT13. We therefore have a system of causal and relative timing relations that must hold in the pulsemode circuit which directly mimic a four cycle handshake.

The consequences of evolving a simple FIFO-like con- 20 troller from a speed-independent to a pulse-mode circuit are summarized in FIG. 15. The different circuits are characterized in terms of robustness, performance, area, power, and testability. In the table shown in FIG. 15, delay is expressed testability is in stuck-at coverage.

The only circuit that contains a hazard-free implementation, even under the specification timing assumptions, is the speed-independent circuit. However the latency of that circuit is from three to five times slower than 30 the circuits that use relative timing. Furthermore, the circuit shown in FIG. 9a is not fully testable, and the testability degrades as the circuit is used in a more restricted environment. The more aggressive timing assumptions tend to increase the performance of the circuit, reduce the area and 35 power, and generally increase the testability. One of the reasons that testability coverage is increased using relative timing is because many of the redundant coverings are removed when the circuits are optimized for time.

Another example of the use of relative timing design can 40 be see in the design of a portion of a variable length instruction decode, here called a "Tag Unit". Decoding of variable length instructions is inherently a serial process, since the length of any instruction directly depends on the lengths of all previous instructions. The performance of 45 instruction length decoding for many computer architectures depends directly on the speed with which this serial decoding operates. A key component in some such architectures is the Tag Unit used to implement the serial ordering of instructions.

A speed-independent tag unit is shown in FIG. 16a. In this example all the interfaces are treated as speed-independent interfaces. The assumption that all the interfaces are speedindependent interfaces means that all the interfaces require request/acknowledge handshakes; this example assumes a 55 four cycle protocol.

Three processes are needed to implement this box:

$PA=r\uparrow.sr\uparrow.sa\uparrow.(sr\downarrow.sa\downarrow|act\uparrow.r\downarrow).a\downarrow.PA$  $PB=sr\uparrow.sa\uparrow(sr\downarrow.sa\downarrow|r\uparrow.a\downarrow).r\downarrow.a\downarrow.PB$ C4=(go0|go1|go2|go3).sa.C4

The two PA processes synchronize the four phase handshake 65 after an r request is received, while the two PB processes are passive and synchronize before handshaking. Therefore,

10

when an irdy and ti request arrives and the bufreq and to cycles have completed, the ti and irdy signals will be acknowledged and the to and bufreq cycles will start. This is accomplished in the specification by renaming the signals and composing the processes as follows:

> IRDY=PA[irdy/r, irdyack/a, go0/sr] TAGIN=PA[ti/r, tia/a, go2/sr] TAGOUT=PB[to/r, toa/a, go3/sr] BUFREQ=PB[bufreq/r, bufack/a, go2/sr] TAGUNIT=(IRDY|TAGIN|TAGOUT|BUFREQ|C4)\{go0, go1, go2, go3, sa}

The implementation of these processes using a program such as ATACS is shown in FIG. 17. Processes PA and PB result in very efficient implementations. The large OR gate, C-element, and the necessity of passing through three state machines from the input to output of the tag path, however, creates significant latency in this implementation.

A more efficient circuit is shown in FIG. 16b. This efficient circuit was derived using relative timing constraints as described above. For instance, the mutex assumption in in pS, energy is in nJ, area is in transistor count and 25 the speed-independent implementation results in the removal of the backward-path handshake for tagin and tagout interfaces. The forward signals are treated as pulses and, therefore, handled as in the FIFO example above. The request and acknowledge protocols on the irdy and bufreq paths are a combination of four cycle and pulse-mode signaling, with irdyack and bufreq being pulses.

> A comparison of the speed-independent circuit of FIG. 16a and the RT circuit of FIG. 16b shows that the RT circuit provides substantial benefit in terms of testability, power, and performance. In real-life applications, the area benefit from this approach may be even higher. For instance, in a microprocessor which can be scaled to reach a higher performance, if slow parts are used, higher scaling factors must be employed to meet the target performance. If the slower SI tag unit is used, for example, the area required would have to balloon significantly if stringent performance goals are to be met.

> In one embodiment, the RT constraints are generated and verified through a version of Analyze that contains support for RT. All the constraints can be attached to an initial process specification as predicates. This simplifies and clarifies both the initial function of the circuit as well as the assumptions required, as each interface can be specified as a simple process with causal synchronization. Representing the complete behavior constraints or timing constraints as a network, as was shown in the FIFO example above, can be helpful for understanding small examples, but can be confusing and impractical for larger, real-world examples such as the Tag Unit.

> In one embodiment, a modified version of a synthesis tool such as Petrify incorporates methods for synthesizing hazard-free circuits under timing assumptions. For instance, in one embodiment, a ".time" parameter has been added in order to convey the relative timing constraints. In addition, in one embodiment an algorithm has been added to the synthesis tool to automatically derive "reasonable" timing assumptions. Finally, in one embodiment, the synthesis tool provides backannotation which indicate the required timing constraints for proper functioning of the circuit. Each of these features will be detailed below.

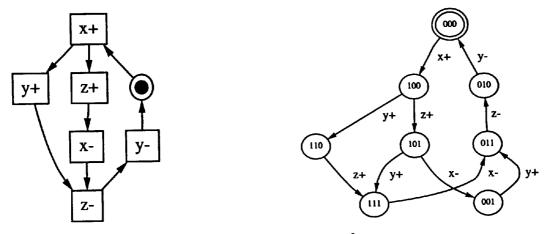

> In one synthesis tool environment, three types of timing assumptions can be specified: firing order of concurrent

events, simultaneous occurrence of concurrent events and early enabling. To properly understand the semantics of relative timing constraints, the concepts of enabling region and firing region must be introduced. Given a state graph, the enabling region of event a, EN(a) is defined as the set of states in which a is enabled. The firing region of event a, FR(a), is defined as the set of states in which a is allowed to

Although in speed-independent circuits both concepts are the same (an event can fire as soon as it is enabled), they 10 differ substantially when timing assumptions are considered. An event can be enabled at some state but cannot fire until the system reaches its firing region. All these timing assumptions are specified in the input file where the STG is described. They should go after the graph (or state graph) 15 specification and before the end statement.

A timing assumption based on the firing order of concurrent events is specified with the following syntax:

The meaning of this statement is the following, "Whenever events a and b are concurrent (i.e. simultaneously enabled and not in conflict), a will always fire before b."

To illustrate how the assumption is made by a synthesis tool such as Petrify we will use the example of FIG. 18. We 25 can observe that events a and b have different relations. They can be concurrent (both enabled in state  $s_0$ ) or ordered (a is enabled in  $s_2$  and b is enabled in  $s_7$ ). The timing assumption only applies to those states in which the events are concurrent

The application of the timing assumption would mean that b will not fire in  $s_0$ . As a consequence, state  $s_1$ , will become unreachable in the timed domain.

With regard to event b, Petrify considers that  $s_0$  is a "don'  $\uparrow$  care" state for the enablement of event b, i.e. after 35 logic synthesis two different solutions could be reported. The first solution would be one in which b is enabled in  $s_0$ . Still, the timing assumptions will make  $s_1$  unreachable, thus b will not fire until  $s_0$  is reached.

The second solution would be one in which b is not 40 enabled in  $s_0$ . In this way, the ordering  $a \rightarrow b$  will be forced by the logic of the circuit, i.e. no timing assumption is required for this solution to be valid.

These two solutions can be formally expressed as follows:

$${s_6}=FR(b)\subseteq EN(b)\subseteq {s_0, s_6}$$

and Petrify will choose a solution for EN(b) that minimizes the cost of the logic.

A timing assumption based on the simultaneous occurrence of concurrent events is specified with the following 50 syntax:

An example of this assumption is shown in FIG. 19. The meaning of the simultaneity timing assumption is the 55 following, "Let us take the states in which a and b are enabled and concurrent. Event c will not fire in any of the successor states until a and b have fired. This assumption only applies when c is triggered by either a or b or both."

Informally, this assumption describes the situation in 60 which the firing time difference between a and b is not distinguishable by event c. Looking at the example, this would mean that the system would produce the same observable behavior if c would be "triggered" by b or by both events a and b.

Looking at the state graph of FIG. 19, the simultaneity constraint indicates that c would not fire in state  $s_6$  and,

12

therefore, state  $s_5$  would become unreachable. On the other hand, event c would be allowed to be enabled in the states  $s_1$ ,  $s_4$  and  $s_6$ . Thus,

$${s_4}=FR(c)\subseteq EN(c)\subseteq {s_1, s_4, s_6}$$

The simultaneity timing assumptions can be extended to larger number of events as follows:

meaning that the firing time of events a, b, c and d is considered to be non-distinguishable with respect to events x, y and z.

A timing assumption based on early enabling is specified with the following syntax:

An example of this assumption is shown in FIG. 20. The formal meaning of this assumption is the following, "Let us take all those states s-I in which c is not enabled, but becomes enabled after firing b (i.e., b triggers c). Then the states  $s_1$  can potentially belong to EN(c)."

Informally, this assumption indicates that event c can be enabled before it must fire. The delay of the logic implementing c will, however, ensure that c will fire after b. Indeed, this may be seen as a risky assumption, since the logic of signals b and c are not known before logic synthesis. Relative timing assumptions therefore require a post-verification to ensure their validity. If they do not hold after synthesis, some after must be taken. For example, the designer could resynthesize the circuit without the invalid assumptions or change the delays of the components of the circuit (e.g., by transistor sizing or delay padding) so that the assumptions become valid.

In the previous example, EN(c) and FR(c) are defined as follows:

$$\{s_6,\,s_8\}\text{=}FR(c)\underline{\subset}EN(c)\underline{\subset}\{s_3,\,s_4,\,s_6,\,s_8\}$$

The early enabling assumptions can be extended to chains of events. In the previous example, the following assumptions could also be specified:

45

indicating that EN(c) can be extended up to the enabling of event a. However, no assumption is made about the enablement of b with regard to a.

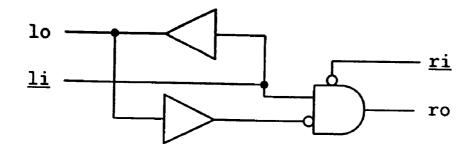

Timing assumptions can be used in Petrify to synthesize the well-known xyz example shown in FIG. 21. A speedindependent implementation of the behavior with complex gates would be the following:

$$[x]=z'(x+y');$$

[y]=x'z';

$$[z]=y'z+x;$$

Assume that x, y and z are output signals and that the firing of y+ always occurs before the firing of x-. This can be deduced intuitively from FIG. 21 by observing that y+ is always enabled before x- and that the logic for signal x in the speed-independent implementation looks more complex than the logic for signal y. (All of these assumptions will, of course, be verified after synthesis of the circuit.)

Based on these assumptions, the following timing assumption can be added to the behavioral specification:

.graph

```

x+y+z+

z+x-

y+z-

z-v-

y-x+

.marking \{<y-,x+>\}

.time y+<|x-

end

```

A circuit can then be synthesized with the following command:

```

petrify xyz.g -cg -topt -eqn xyz.eqn -no

```

where the option "<topt" indicates that Petrify must take timing assumptions into consideration to derive logic. The following logic is obtained:

```

[x]=z'(x+y');

[y]=x'z';

[z]=x;

```

The synthesized logic is a drastic simplification of the logic for signal z. Petrify has taken advantage of the timing assumption to consider the state 001 as unreachable and 25 implement z as a simple buffer.

But as important as the solution is the feedback that Petrify gives about the timing assumptions used for each solution. In one embodiment, file petrify.log includes different solutions for each signal. In one such embodiment, the 30  $\overline{x = y'}$ following solutions are reported for signal z:

```

z = x

>triggers(SET):

x + -) z +

>triggers(RESET):

x- -) z-

>4 transistors (2 n, 2 p)

>Estimated delay: rising = 18.19, falling = 29.19

>Speed independent (no timing assumptions)

```

The first solution corresponds to the one obtained with timing assumptions. The second one corresponds to the speed-independent implementation. There are two important pieces of information reported for the solutions: timing assumptions and trigger signals.

In the embodiment shown, Petrify indicates under timing assumptions that the solution z=x is only valid under the assumption that y+ fires before x. In contrast, the solution z=y'z+x is valid under any timing assumption (i.e., it's speed-independent). In one embodiment, the timing assump- 50 tions reported by Petrify are not always the same as any timing assumptions that are part of the specification. Instead Petrify will try to report the less stringent assumptions that make the solution valid.

Under trigger signals, in one embodiment, Petrify indi- 55 cates which events are triggered by the rising and falling transitions of the signal. Note the difference for the trigger events of z-. In the "timed" solution, y+ is no longer triggering z- since it is assumed to fire before x-. This information is much more relevant when "early enabling" assumptions are done for synthesis.

Another type of timing assumption can be made. For instance, in the xyz circuit y+ and z+ are enabled simultaneously. If the delays of their gates would be similar, we could consider that the firing time of y+ and z+ would not 65 This indicates that x- is enabled in such a way that it be distinguishable with respect to event x-. The specification would now read as follows:

```

.outputs x y z

.graph

X+Y+Z+

z+x-

y+z-

x-z-

z-v-

y-x+

.marking \{<y-,x+>\}

.time y+=z+\#x-

.end

```

After executing the same command as above, the following solution is obtained:

```

[x]=y';

[y]=x'z';

[z]=x;

```

Any timing assumptions that are algorithmically generated or based on simultaneous enablings may not result in correct solutions and must be checked for validity. Again, in one embodiment the file petrify.log will provides relevant information about timing assumptions. In one such embodiment the file petrify.log contains a number of solutions for x. These solutions can be compared to the speed-independent solution (in "other solutions"):

```

>triggers(SET): y- -) x+

>triggers(RESET): y+ -) x-

>2 transistors (1 n, 1 p)

>Estimated delay: rising = 13.44, falling = 10.75

>Concurrency reduction: y+==>x-

>Timing assumptions (early enabling): z+<x-

x = y'z'

>triggers(SET): v- -) x+

>triggers(RESET): (y+, z+)-) x-

>4 transistors (2 n, 2 p)

>Estimated delay: rising = 27.50, falling = 11.00

>Timing assumptions (early enabling): z+<x-

[... other solutions ...]

>triggers(SET): y- -) x+

>triggers(RESET): z+ -) x-

>8 transistors (4 n, 4 p)

>Estimated delay: rising = 29.38, falling = 11.00

>Speed independent (no timing assumptions)

```

The solution x=y' is generated by disabling x- in state 101 (where it was initially enabled). This makes states 001 unreachable. But note that, in this case, it is not unreachable due to timing assumptions, but due to the fact that the logic for x does not enable x- in state 101. This is what the message

```

>Concurrency reduction: y+==>x+

```

means. In other words, the fact that y+ fires before x- fires does not need to be verified by making timing assumptions. It is something that the logic of the circuit already guaran-

Still, there is another important assumption for that solution:

```

>Timing assumptions (early enabling): z+<x-

```

becomes concurrent with z+ (now x- is also enabled in state 110). The assumption for correctness is that z+ should fire

before x-. To verify that assumption at circuit level, one might need some additional information, i.e., how much early is x- enabled? Again, that information is provided in the section of trigger signals. We may realize that now it is y+ that triggers x- (it was z+ in the speed-independent solution). Thus, by combining these pieces of information one can determine when the enabling of an event is started (trigger events) and when the event is allowed to fire (when other concurrent events have already fired). Now, it is time for the designer to decide whether these assumptions are realistic or can be met by the implementation.

Still, there is another interesting solution that appears in the file petrify.log, i.e., x=y'z'. This solution makes the state 001 again reachable, since x- is enabled in state 101. But x- is also enabled earlier in state 110 and the assumption z+<x- must still be met.

In one embodiment, an important aspect of the information provided by the relative timing implementation of Petrify is that different timing assumptions must be ensured for each different solution of each signal. The selection of one solution for one signal does not affect the assumptions 20 made for other gates. However, the combination of all the solutions for each gate may lead to a set of simpler constraints. In the embodiment of Petrify described above, it is still up to the designer to figure out how the constraints interact. What this embodiment of Petrify does guarantee is 25 that the solutions will be valid if the timing assumptions reported for each individual solution of each signal are met.

In one embodiment, Petrify makes an attempt to automatically generate "reasonable" timing assumptions. Since a number of assumptions are easily derivable by inspection of 30 the structure of the specification, such an approach allows the designer to work mainly in the area of improving the performance of the circuits. That is, Petrify is a tool for simplifying the job of the designer and not a designer substitute. Indeed, in one embodiment, Petrify identifies the assumptions which have been generated automatically and those assumptions that are actually used for each solution. It is then the designer's responsibility to guarantee the validity of the timing assumptions.

The following model is considered for the delay of a  $_{40}$  signal transition (delay from its enabling time to its firing time):

Non-input signals: each gate implementing a non-input signal has a delay in the interval  $[1-\epsilon, 1+\epsilon]$ , where  $\epsilon < \frac{1}{3}$ . Thus, the delay of two gates is always greater than the 45 delay of one gate.

Input signals: have a delay in the interval  $[1+\epsilon, \infty]$ . Thus, the delay of the environment is always greater than the delay of one gate.

Slow input signals: have a delay in the interval  $[k, \infty]$ , where 50 k is any arbitrarily large constant. The delay k indicates that the enabling of a slow input signal transition always allows the completion of any internal activity in the circuit (e.g., firing of enabled non-input signals).

Delay padding: the delay of any gate implementing any 55 non-input signal can be lengthened after logic synthesis, e.g. by transistor sizing or delay padding, to meet the required timing assumptions.

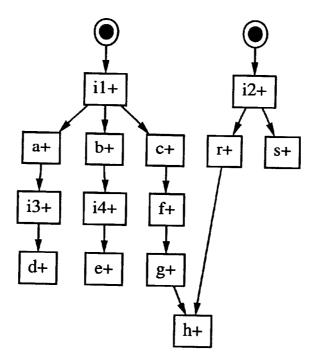

The automatic generation of timing assumptions by using this delay model will be illustrated with the example of FIG.  $_{60}$  22, where  $i_1, \ldots i_4$  are input signals and where the remaining signals are output signals. Moreover, the event  $i_4$ + is declared to be "slow" by using the statement:

.slow i4+

The assumptions made on the relative order of two concurrent events, a and b are the following:

1) If a is always enabled before b and a is not an input event, then a is assumed to fire before (.time a <|b ). In the example of FIG. 22 this assumption would apply, among others, to the pairs of events a→i<sub>4</sub>+ and b+→g+.

16

- 2) If a and b are simultaneously enabled, a is a non-input event and b is an input event, then a is assumed to fire before (.time a<|b ). There is no such case in the example of FIG. 22, but it would correspond to the pair of events a→b+ if b was an input event.</p>

- 10 3) If a and b are simultaneously enabled and both are non-input events, Petrify selects heuristically an order between both (typically this order determines that the event with simpler logic will fire first, although it may not be necessarily true when the actual gates are derived after logic synthesis).

- 4) No assumptions are done for pairs of events that can be enabled in different order in the untimed domain. For example, for events i<sub>4</sub>+ and f+ we can find event traces in which i<sub>4</sub>+ is enabled first (e.g., i<sub>1</sub>+, b+, c+) and in which f+is first enabled (e.g., i<sub>1</sub>+, c+, b+).

In one embodiment, if two non-input events, a and b, are enabled simultaneously and another event c is triggered by a or b (or both), a simultaneity assumption is automatically generated (a=b@c). In one such embodiment, Petrify makes this analysis only for pairs of simultaneous events. Assumptions on more than two simultaneous events are left to be specified by the designer. There are several examples of simultaneity assumptions in FIG. 22 (e.g., b+=c+@f+ and t+=s+@h+).

In one embodiment, when several non-input events have a trigger relation among them, Petrify automatically generates early enabling assumptions, taking into account that the delays of the gates can be properly lengthened to meet the ordering relations of the specification. In the example of FIG. 22, there are chains of events that have a trigger relation among them (e.g.,  $c+\rightarrow f+\rightarrow g+\rightarrow h+$  and  $r+\rightarrow h+$ ). The following assumptions are automatically generated:

.time f+>c+

.time g+>f+>c+

.time h+>g+>f+>c+

In one embodiment, ordering of slow input events is a generalization of the fundamental mode assumption. In one embodiment, Petrify is designed with the constraint that the delay of slow input events is long enough to enable the circuit stabilize when other internal activity is in process. Because of this constraint, Petrify can automatically generate assumptions on the firing order of slow events.

In one such embodiment, timing analysis is performed in such a way that only concurrent non-input events having a common predecessor history with the slow input event are assumed to fire first. This intuitive idea will be more clear after looking at the example in FIG. 22, where only i<sub>4</sub>+ is a slow input event.

It can be seen by examining FIG. 22 that events  $i_4+$  and g+ have a common predecessor event in their history:  $i_1+$ . Moreover, no other input events precede the enablement of  $i_4+$  and g+ since the firing of  $i_1+$ . If the firing time of  $i_1+$  is treated as the starting point for timing analysis (i.e., t=0), the delay model for automatic assumptions indicates that g+ will fire in the interval  $[3(1-\epsilon), 3(1+\epsilon)]$ , i.e., three gate delays. On the other hand, the firing interval for  $i_4+$  will be in the interval  $[k+1-\epsilon, \infty)$ , where k can be arbitrarily large. Therefore, Petrify will deduce that the firing time for g+ will be always before the one for  $i_4+$ .

17

Note that this assumption does not hold when the considered event is h+since  $i_4$ + and g+ have no common predecessor event in their history. For a similar reason, no ordering assumption can be made for the firing of  $i_4$ + and d+ since an input event ( $i_3$ +) precedes d+ before meeting the  $i_1$ + 5 common preceding event.

Technically, this common point in the history of two events is called local nodal point. An analysis based on local nodal points generalizes the concept of fundamental node typically used for the synthesis of burst-mode specifications. 10 Burst-mode machines work under the assumption that each state of the specification is a global nodal point, i.e. no non-input activity is enabled in the state. From the point of view of specification, fundamental mode does not allow any concurrency between the environment and the circuit.

The notion of a slow input event takes advantage of fundamental mode assumptions (i.e., logic can be simplified) and speed-independent assumptions (i.e., concurrency is not sacrificed). As an example, the definition of slow input events allows the synthesis of a system having 20 several sets of handshake signals. It does this by assuming a "local") fundamental mode operation with each individual handshake, but by also maintaining the concurrency among different independent sets of handshakes. One of these examples is the VME bus controller described in the next 25 section.

Finally, all the automatically generated assumptions for the example of FIG. 22 are listed below:

```

.time b+<|a+

.time c+<|a+

.time a+<|i4+

.time a+<|e+

.time a+<|f+

.time a+<|g+

.time a+<|h+

.time c+<|b+

.time b+<|i3+

.time b+<|d+

.time b+<|f+

.time b+<|g+

.time b+<|h+

.time c+<|i3+

.time c+<|d+

.time c+<li4+

.time c+<|e+

.time s+<|h+

.time s+<|r+

.time a+<|i4+

.time c+<|i4+

.time f+<|i4+

```

.time g+<|i4+

```

.time f+>c+

.time g+>f+>c+

.time h+>g+>f+>c+

.time h+>r+

.time a+=c+@f+

.time b+=c+@f+

.time r+=s+@h+

```

Even though the xyz example is simple, significant improvements in logic can be obtained by applying automatic timing assumptions on it. For the xyz example shown in FIG. 21 and without any timing assumption, one would execute the command:

```

petrify xyz.g -cg -atopt -eqn xyz.eqn -no

```

The option "-atopt" indicates that Petrify must generate automatic timing assumptions. In the situation where the designer has already specified some assumptions, the new ones are added to the designer's ones. In any case, Petrify takes care that the assumptions automatically generated are not contradictory with the ones specified by the designer. The resulting circuit is shown in FIG. 23.

The circuit shown in FIG. 23 is the solution reported by Petrify in the file xyz.eqn. Since the timing assumptions were generated algorithmically they must be examined for validity. In one embodiment, this can be done by examining the file petrify.log. For instance, in one embodiment the following assumptions have been automatically generated:

```

.time z+ < v+

#concurrency reduction (automatic & simultaneous)

time y+ <|x-

#concurrency reduction (automatic)

time x+>y->x->y+

#early enabling (automatic)

#early enabling (automatic)

.time x+>y->z-

.time x->z+

#early enabling (automatic)

.time z->y+

#early enabling (automatic)

#early enabling (automatic)

.time z->x-

#early enabling (automatic)

.time y->z-

.time y->z->z+

#early enabling (automatic)

#simultaneity (automatic)

.time v+=z+@x-

```

and the following information is reported for the solutions:

```

x = y'

>triggers(SET): y- -) x+

>triggers(RESET): y+ -) x-

>2 transistors (1 n, 1 p)

>Estimated delay: rising = 13.44, falling = 10.75

>Concurrency reduction: y+==>x-

>Timing assumptions (early enabling): z+<x-

y = z

>triggers(SET): z+ -) y+

>triggers(RESET): z- -) y-

>4 transistors (2 n, 2 p)

60

>Estimated delay: rising = 18.19, falling = 16.69

>Concurrency reduction z+==>y+

>Speed independent (no timing assumptions)

z = x

65

>triggers(SET): x +-) z+

>triggers(RESET): x - -) z-

```

18

### -continued

>4 transistors (2 n, 2 p) >Estimated delay: rising = 18.19, falling = 16.69 >Timing assumptions (concurrency): y+<x-

The timing information can be summarized as follows:

- 1) The firing order z+→y+ is required for the solution x=y' to be valid, but the firing order z+→y+ is enforced by the solution y=z that reduces concurrency and makes the state 110 unreachable; and

- 2) The firing order y+→x- is required for the solution z=x to be valid, but the firing order y+→x- is enforced by the solution x=y' that reduces concurrency and makes the state 001 unreachable.

The enforced concurrency reduction therefore ensures the validity of the timing assumptions and a speed-independent circuit is obtained. This, therefore, is an example on how concurrency reduction does not always imply a loss of performance. The reduction of logic results in a more efficient circuit.