### US005202987A

## United States Patent [19]

## Bayer et al.

#### Patent Number: [11]

5,202,987

## Date of Patent:

Apr. 13, 1993

## [54] HIGH FLOW-RATE SYNCHRONIZER/SCHEDULER APPARATUS AND METHOD FOR MULTIPROCESSORS

[76] Inventors: Nimrod Bayer, 7 Gordon Street,

Givataim; Ran Ginosar, Nofit 104

(near Tivon), both of Israel

[21] Appl. No.: 641,250

[56]

[22] Filed: Jan. 15, 1991

[30] Foreign Application Priority Data

| F    | eb. 1, 1990 [IL] | Israel 093239                      |

|------|------------------|------------------------------------|

| [51] | Int. Cl,5        | G06F 15/16                         |

|      | U.S. Cl          | 395/650; 364/DIG. 1;               |

|      | 364/281.         | 8; 364/230.3; 364/271.3; 364/228.3 |

| [58] | Field of Search  |                                    |

### References Cited

## U.S. PATENT DOCUMENTS

| 4,333,144 | 6/1982  | Whiteside et al | 364/DIG. 1 |

|-----------|---------|-----------------|------------|

|           |         | Bourrez         |            |

| 4,779,194 | 10/1988 | Jennings et al  | 364/DIG. 1 |

|           |         | Inoue           |            |

| 4,967,326 | 10/1990 | May             | 366/DIG. 1 |

| 4,985,831 | 1/1991  | Dulong et al    | 364/DIG. 1 |

## OTHER PUBLICATIONS

"The Effect of Operation Scheduling on the Performance of a Data Flow Computer" M. Gransky et al., IEEE Transactions on Computers, vol. C-36, No. 9, Sep. 1987, pp. 1019-1029.

"High-Performance Computer Architecture", H. S. Stone, Addison-Wesley Publishing Co., 1987, pp. 347-365.

"Execution of Parallel Loops On Parallel Processor Systems", C. D. Polychronopoulos et al., Proc. Int. Conf. on Parallel Processing, 1986, pp. 519-527.

"A Technique For Reducing Synchronization Overhead In Large Scale Multiprocessors", Z. Li et al, Proc. of the 12th Symp. on Computer Architecture, 1985, pp. 284-291.

"The Piecewise Data Flow Architecture: Architectural Concepts", J. E. Requa et al., IEEE Trans. on Computers, vol. C-32, No. 5, May 1983, pp. 425-438.

"A Case Study in the Application of a Tightly Coupled

Multiprocessor to Scientific Computations", N. S. Ostlund et al., Parallel Computations, G. Rodrigue, editor, Academic Press, 1982, pp. 315-364.

"Synchronized and Asynchronous Parallel Algorithms For Multiprocessors", H. T. Kung, Algorithms and Complexity, Academic Press, 1976, pp. 153-200 (reprinted with permission by Department of Computer Science, Carnegie-Mellon University, Pittsburgh, Pa., pp. 428-463).

"A Survey of Synchronization Methods for Parallel Computers", A. Dinning, IEEE Computer, vol. 20, No. 19, Jan. 1987, pp. 100-109.

"Synchronization, Coherence, and Event Ordering in Multiprocessors", M. Dubois et al., IEEE Computer, vol. 21, No. 2, Feb. 1988, pp. 9-22.

"The NYU Ultracomputer-Designing an MIMD Shared Memory Parallel Computer", A. Gottlier, et al., IEEE Trans. on Computers, Feb. 1983, pp. 175-189 (reprinted with permission by the Courant Institute of Mathematical Sciences, New York University, New York as pp. 276-290).

(List continued on next page.)

Primary Examiner-Thomas M. Heckler Attorney, Agent, or Firm-Morgan & Finnegan

### **ABSTRACT**

A high flow-rate synchronizer/scheduler apparatus for a mutiprocessor system during program run-time, comprises a connection matrix for monitoring and detecting computational tasks which are allowed for execution containing a task map and a network of nodes for distributing to the processors information or computational tasks detected to be enabled by the connection matrix. The network of nodes possesses the capability of decomposing information on a pack of allocated computational tasks into messages of finer sub-packs to be sent toward the processors, as well as the capability of unifying packs of information on termination of computational tasks into a more comprehensive pack. A method of performing the synchronization/scheduling in a multiprocessor system of this apparatus is also described.

## 10 Claims, 4 Drawing Sheets

### OTHER PUBLICATIONS

"Cm\*—A modular, multi-microprocessor", R. J. Swan, et al., AFIPS Conf. Proc., 1977 National Computer Conference, pp. 637-644.

"Architecture and Applications of the HEP Multiprocessor Computer System", B. J. Smith, Real Time Signal Processing IV, Proceedings of SPIE, Aug. 1981, pp. 241-248 (reprinted as pp. 231-238).

"The IBM Research Parallel Processor Prototype (RP3): Introduction and Architecture", G. F. Pfister et al., Proc. Int. Conf. on Parallel Processing, Aug. 1985, pp. 764-771.

"Cedar", D. Gajski et al., Report No. UIUCDCS-R-8-3-1123, Department of Computer Science, University of Illinois, Urbana, Feb. 1983, pp. 1-25 (reprinted as pp. 251-275).

"A Synchronization Scheme and Its Applications for Large Multiprocessor Systems," C. Q. Zhu, Proc. 4th Int. Conf. on Distributed Computing Systems, 1984, pp. 486–493.

"The Butterfly Parallel Processor", W. Crowther et al., Newsletter of the Computer Architecture Technical Committee (IEEE Computer Society), Sep./Dec. 1985, pp. 18-45.

pp. 18-45.

"Efficient Synchronization Primitives for Large-Scale Cache-Coherent Multiprocessors", J. R. Goodman, Proc. of the Conf. on Architectural Support for Programming Languages and Operating Systems, AS-PLOS-III, 1989, pp. 64-75.

"Guided Self-Scheduling: A Practical Scheduling Scheme for Parallel Supercomputers", C. D. Polychronopoulos et al., IEEE Trans. on Computers, vol.

C-36, No. 12, Dec. 1987, pp. 1425-1439.

"A Controllable MIMD Architecture", S. F. Lundstrom et al., Proceedings of the 1980 International Conference on Parallel Processing, pp. 19-27 (reprinted by Burroughs Corporation, Paoli, Pa. as pp. 165-173). "The Fuzzy Barrier: A Mechanism for High Speed

"The Fuzzy Barrier: A Mechanism for High Speed Synchronization of Processors", R. Gupta, Proc. of the Conf. on Architectural Support for Programming Languages and Operating Systems, ASPLOS-III, 1989, pp. 54-63.

"A Hardware Task Scheduling Mechanism for Real-Time Multi-Microprocessor Architecture", A. D. Hurt et al., Proceedings of the 1982 Real-Time Systems Symposium, pp. 113-123.

"Combining Data Flow and Control Flow Computing", Computer Journal, vol. 25, No. 2, 1982, pp. 207-217.

"NP-Complete Scheduling Problems," J. D. Ullman, J. Comput. Syst. Sci., vol. 10, Jun. 1975, pp. 384-393.

"Computer and Job-Shop Scheduling and Theory", E. Coffman, Wiley Publishers, New York, 1976, p. 58.

"A Hardware-Synchronized/Scheduled Multiprocessor Model", submitted as a M. Sc. Thesis, EE Department, Technion, Israel Institute of Technology, Jan. 1989 (unpublished) pp. 83-92.

"Programming for Parallelism", A. H. Karp, IEEE Computer, vol. 20 No. 5, May 1987, pp. 43-57.

"Introduction to VLSI Systems", C. Mead et al., Addison-Wesley, 1980, chap. 7 pp. 218-254.

"Connectionist Architectures for Artificial Intelligence", S. E. Fahlman et al., IEEE Computer, vol. 20, No. 19, Jan. 1987, pp. 100-109.

U.S. Patent

5,202,

## HIGH FLOW-RATE SYNCHRONIZER/SCHEDULER APPARATUS AND METHOD FOR MULTIPROCESSORS

1

### FIELD OF THE INVENTION

The present invention relates to an architectural solution to the problem of accomplishing efficient synchronization, scheduling and work allocation in multiprocessors.

### **BACKGROUND OF THE INVENTION**

The coordination of multiple operations in shared memory multiprocessors often constitutes a substantial performance bottleneck. Process synchronization and scheduling are generally performed by software, and managed via shared memory. Execution of parallel programs on a shared-memory, speedup-oriented multiprocessor necessitates a means for synchronizing the activities of the individual processors. This necessity arises due to precedence constraints within algorithms: When one computation is dependent upon the result of other computations, it must not commence before they finish. In the general case, such constraints are projected onto an algorithm's parallel decomposition, and 25 reflected as precedence relations among its execution threads.

Synchronization is only one aspect of a broad activity, which may be termed parallel operation coordination, whose other aspects are scheduling and work allo- 30 cation. Scheduling is selecting an execution order for the operations of a program, out of a space of execution orders which are feasible under the given architecture and precedence constraints, as described in the paper entitled "The Effect of Operation Scheduling on the 35 Performance of a Data Flow Computer," M. Gransky et al, IEEE Trans. on Computers, Vol. C-36 No. 9, September 1987, pp. 1019-1029. While scheduling deals with the point of view of the tasks to be computed. work allocation deals with the point of view of the 40 processors which carry out the tasks. Thus, the distinction between scheduling an allocation is not clear-cut, and some researchers use these terms interchangeably. The decisive questions may be posed as follows: "which ready-to-run piece of work should be executed first ?" 45 which is a matter of scheduling policy; questions of the sort "to which processor should a given piece of work be allocated?" or "how much work should be allocated at once to a given processor?", are considered to be a matter of allocation policy. Scheduling and allocation 50 may be static, i.e. determined before program run-time.

In fully dynamic systems, all these coordination activities are not an inherent part of the actual computation, but are rather designed to support it. Since they consume computational resources, they are considered 55 as overhead. Coordination or synchronization efficiency, refers to the efficiency of parallel operation coordination activity itself, excluding the indirect effects of scheduling policy.

The overall multiprocessor performance is influenced 60 significantly by the efficiency of coordination, as described in the book entitled "High-Performance Computer Architecture", H. S. Stone, Addison-Wesley, 1987, and in the papers entitled "Execution of Parallel Loops on Parallel Processor Systems," C. D. Polychronopoulos et al, Proc. Int. Conf. on Parallel Processing, 1986, pp. 519-527: "A Technique for Reducing Synchronization Overhead in Large Scale Multiproces-

sors", Z. Li et al. Proc. of the 12th Symp. on Computer Architecture, 1985, pp. 284-291; "The Piecewise Data Flow Architecture: Architectural Concepts," J. E. Requa et al. IEEE Trans. on Computers, Vol. C-32 No. 5 5, May 1983, pp. 425-438; "A Case Study in the Application of a Tightly Coupled Multiprocessor to Scientific Computations" N. S. Ostlund et al. Parallel Com-

cation of a Tightly Coupled Multiprocessor to Scientific Computations," N. S. Ostlund et al, Parallel Computations, G. Rodrigue, editor, Academic Press, 1982, pp. 315-364; "Synchronized and Asynchronous Parallel Algorithms for Multiprocessors," H. T. Kung, Algorithms and Complexity, Academic Press, 1976, pp. 153-200; and "A Survey of Synchronization Methods for Prallel Computers," A Dinning, IEEE Computer, Vol. 20 No. 19, January 1987, pp. 100-109.

Inefficiencies in these processes are manifested in overhead-activity and overhead-idling. The former is the activity which is required, once a task has been computed, to obtain a new piece of productive work, while the latter is due to contention of synchronization resources, which are system-global by nature.

Overhead-idling is principally caused by insufficient synchronization rate capability. As noted in the text by H. S. Stone supra, this capability (expressed in MSYPS, Millions of Synchronizations Per Second) constitutes an independent architectural measure; in particular, it is not necessarily proportionate to the system's overall raw processing power, as expressed MIPS and MFLOPS. Decompositing a given algorithm into ever finer granularity levels will yield an ever increasing demand for synchronization rate, and an ever bigger ratio of overhead-activity to productive computation. Thus, at some level of granularity, synchronization may become a bottleneck, thereby practically limiting the exploitable level of parallelism. Consequently, it is desirable to search for means to increase the synchronization rate capability and to reduce the coordination overhead activity of multiprocessor systems.

Synchronization methods for multiprocessors were born out of mutual exclusion methods, prevalent in multiprogrammed uniprocessors. Still, synchronization is usually implemented around special synchronization data in main memory, as described in the paper entitled "Synchronization, Coherence, and Event Ordering in Multiprocessors," M. Dubois et al, IEEE Computer, Vol. 21 No. 2, February 1988, pp. 9-22. These synchronization data are either stand-alone (e.g. locks and semaphores), or attached to regular data objects (such as presence bits). A variety of synchronization primitives, such as Test & Set or Fetch & Add. serve to establish access to synchronization variables and to manipulate them, as described in the paper entitled "The NYU Ultracomputer-Designing an MIMD shared Memory Parallel Processor," A. Gottlieb et al. IEEE Trans. on Computers, February 1983, pp. 175-89. The implementation of these primitives is based on some special hardware support, whether rudimentary or massive. Yet the essential levels of parallel operation coordination are implemented in software. Some examples of prominent commercial and research multiprocessors which are included in this framework are described in the following papers: "Cm\*-A modular multi-microprocessor," R. J. Swan et al, AFIPS Conf. Proc., 1977 National Computer Conference, pp. 637-644; "Architecture and Applications of the HEP Multiprocessor Computer System," B. J. Smith, Real Time Signal Processing IV, Proceedings of SPIE, August 1981, pp. 241-248; "The IMB RP3 Introduction and Architecture," G. F. Pfister

2

et al. Proc. Int. Conf. on Parallel Processing, August 1985, pp. 764-771; "Cedar", D. Gajski et al, Report No. UIUCDCS-R-83-1123. Department of Computer Science, University of Illinois, Urbana, February 1983, pp. 1-25; "Synchronization Scheme and its Applications for 5 Large Multiprocessor Systems," C. Q. Zhu Proc. 4th Int. Conf. on Distributed Computing Systems, 1984, pp. 486-493; and "The Butterfly Parallel Processor," W. Crowther et al. Newsletter of the Computer Architecture Technical Committee (IEEE Computer Society), 10 September/December 1985, pp. 18-45. Within this framework, efforts are aimed at improving synchronization efficiency were routed to the following directions: Development of enhanced hardware support for synchronization primitives (most notably - NYU Ultracom- 15 puter's combining network, as described in the paper by Gottlieb, supra.); development of more powerful synchronization primitives as described in the paper by C. Q. Zhu et al supra, and the paper by J. R. Goodman entitled "Efficient Synchronization Primitives for 20 Large-Scale Cache-Coherent Multiprocessors," Proc. of the Conf. on Architectural Support for Programming Languages and Operating Systems, ASPLOS-III, 1989, pp. 64-75; development of inherently asynchronous 25 parallel algorithms, as described in the paper by H. T. Kung supra; and development of various techniques for synchronization minimization, as described in the paper by Z. Li et al, and in the paper entitled "Guided Self-Scheduling: A Practical Scheduling Scheme for Paral- 30 lel Supercomputers," C. D. Polychronopoulos et al, IEEE Trans. on Computers, Vol. C-36 No. 12, December 1987, pp. 1425-1439.

A recent survey of synchronization methods conthe synchronization mechanisms of seven machines. While giving a classification for prevalent synchronization methods, the paper by Dinning supra confirms the central and basic role of protocols for synchronized access to shared data in all these methods (except in 40 sors, 'puristic" message passing).

Synchronization mechanisms which exceed the framework described above, while promoting the role of hardware, have been proposed by various researchers. Some of these proposals are aimed at hardware 45 implementations of barrier synchronization or synchronized wait, as described in the papers entitled "A Controllable MIMD Architecture," S. F. Lundstrom et al, Proceedings of the 1980 International Conference on Parallel Processing, pp. 19-27 and "The Fuzzy Barrier: 50 A Mechanism for High speed Synchronization of Processors," R. Gupta, Proc. of the Conf. on Architectural Support for Programming Languages and Operating Systems, ASPLOS-III, 1989, pp. 54-63. A more general hardware mechanism, which is aimed at arbitrary paral- 55 lelism patterns, is based on routing of control tokens, but is oriented towards essentially static work allocation, is proposed in the paper entitled "A Hardware Task Scheduling Mechanism for Real-Time Multi-Microprocessor Architecture," A. D. Hurt et al, Pro- 60 ceedings of the 1982 Real-Time Systems Symposium, pp. 113-123. A centralized synchronization/scheduling facility, targeted at arbitrary parallelism patterns and at dynamic allocation and scheduling, was argued for in the paper by D. Gajski supra, but no specific architec- 65 ture was proposed.

Therefore, it would be desirable to provide a global synchronization/scheduling unit which is capable of dynamic allocation and scheduling in a multiprocessor system.

### SUMMARY OF THE INVENTION

Accordingly, it is a principal object of the present invention to overcome the above-mentioned disadvantages of the prior art, and provide apparatus for accomplishing a high synchronization/scheduling rate, adequate for massively parallel multiprocessors.

It is another object of the invention to provided the synchronization/scheduling apparatus with the capability of fast detection of events where dormant computational tasks become allowed for execution.

It is still a further object of the invention to provide a global synchronization/scheduling subsystem which offloads synchronization/scheduling-related overhead activity from the processors.

In accordance with a preferred embodiment of the present invention, there is provided a hardware synchronization/scheduling apparatus for performing synchronization/scheduling in a multiprocessor system by controlling, during program run-time, a process of monitoring and detecting which computational tasks are allowed for execution and allocating computational tasks to processors, the tasks being represented by instructions and data accessible to the processors via instruction and data storage hardware, said synchronization/scheduling apparatus comprising:

means for monitoring and detecting which computational tasks are allowed for execution, said monitoringdetecting means containing a task map describing the precedence relations among the computational tasks of the program; and

communication/distribution means for distributing, tained in the paper by Dinning supra, describes in detail 35 to the processors, information on computational tasks detected by said monitoring/detecting means to be allowed for execution and for forwarding, to said monitoring/detecting means, information on termination of execution of computational tasks at the proces-

Said communication/distribution means comprising a network of nodes processing both the capability of decomposing information on a pack of allocated computational tasks into messages of finer sub-packs of allocated computational tasks to be sent toward the processors, and possessing the capability of unifying packs of information on termination of computational tasks into a more comprehensive pack, to be sent to said means for monitoring/detecting of allowed computational tasks.

In the preferred embodiment, the proposed architecture adds a synchronization/scheduling subsystem to the multiprocessor subsystem. This consists of a central unit and an active distribution network controlling the multiple processors. The synchronization/scheduling subsystem is programmed with the complete synchronization and scheduling information for the executed parallel algorithm.

The synchronization/scheduling subsystem comprises a task map which contains dependencies between tasks to be performed by the processors. The code of the tasks is loaded in the shared memory space, whereas the topology of the task map is held by the synchronizer/scheduler. The latter uses the task map for allocating tasks to the processors. While doing so, it continuously monitors the employment state of the processors, and makes allocations dynamically and on the basis of processor availability. A task is allocated by signalling its identification information across the link

between the synchronizer/scheduler and the designated processor. Further parameters, or data to be processed by the task, may be acquired from the shared memory.

When allocated a task, a processor is caused to restart, with the first instruction fetch address determined 5 by the task's identity. The processor then proceeds in executing instructions fetched from memory, until encountering an instruction signifying the end of the task. The processor then enters a halted state, exporting an indication of its new state to the synchronizer/- 10 scheduler. This indication, when received by the synchronizer/scheduler, serves a twofold function: First, the processor is marked free and ready for another allocation. Secondly, the event of the current task's termination is internally marked, and may cause the 15 enabling of other tasks which depend on the current one. A task is said to be enabled when it is recognized by the system to be allowed for execution. The enabling of a dependent task takes place if all its other input dependencies have already been activated in a similar 20 manner. (OR relations between input dependencies are also possible, and discussed further herein with regard to the architecture's underlying programming model).

In addition to a task map, the synchronizer/scheduler is supplied with the system configuration data. This 25 includes such details as the number of processors, the capabilities of each processor (if processors are not a-priori identical), etc.

Given a set of enabled tasks, as well as processor availability data, the synchronizer/scheduler then per- 30 forms scheduling of those tasks. Any non-random scheduling policy must rely upon some heuristics: Even when task execution times are known in advance, finding an optimal schedule for a program represented as a dependency graph is an NP-complete problem. Most 35 scheduling heuristics are bases on the critical path method, and thereby belong to the class of list scheduling policies; i.e., policies that rely on a list of fixed task priorities. List scheduling can be supported by the inventive scheme described herein, by embedding task 40 priorities in the task map load-module submitted to the synchronizer/scheduler. Whenever an allocation takes place, the allocated tasks are those which have highest priorities amongst the current selection of enabled tasks.

The general architectural concepts described so far 45 may be implemented in multiple alternative ways. The processors may range from minute processing elements to large scientific processors. They are not limited to any specific type, and are not confined to the voning units. The architecture may also be applied to nonhomogeneous systems. The shared memory may consist of physically shared storage, possibly accessed through an interconnection network, or be distributed over the processors, as long as common memory space is pre- 55 served, at least in part.

Other features and advantages of the invention will become apparent from the following drawings and description.

## BRIEF DESCRIPTION OF THE DRAWINGS

For a better understanding of the invention with regard to the embodiments thereof, reference is made to the accompanying drawings in which like numerals designate corresponding elements or sections through- 65 No. 2, 1982, pp. 207-217, it may rather be referred to as out, and in which:

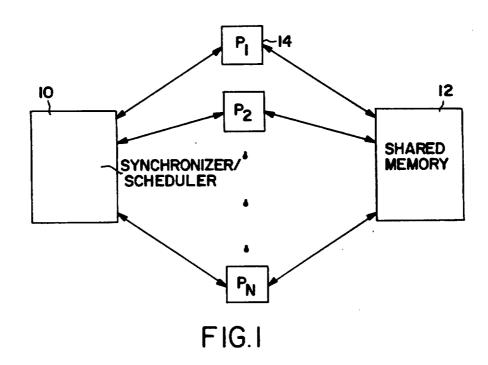

FIG. 1 shows a multiprocessor system architecture featuring a synchronizer/scheduler apparatus con-

6 structed and operated in accordance with the principles of the present invention;

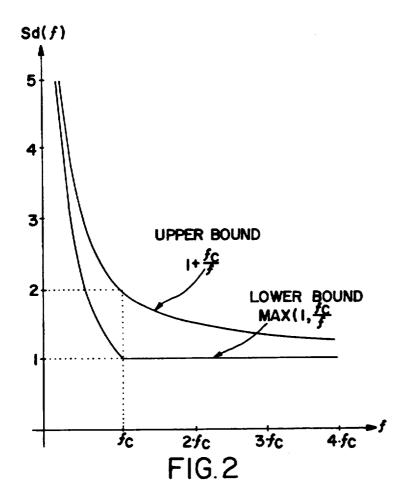

FIG. 2 is a graph illustrating bounds on the overall slowdown in program execution as a function of the available synchronization/scheduling rate capability;

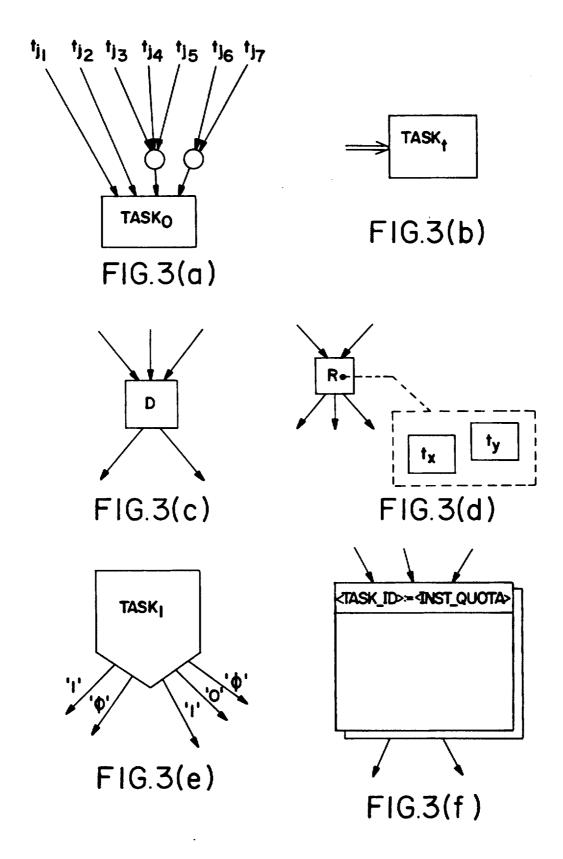

FIGS. 3a-f show graphical notations for programming features associated with a programming model useful in constructing a task map for multiprocessor

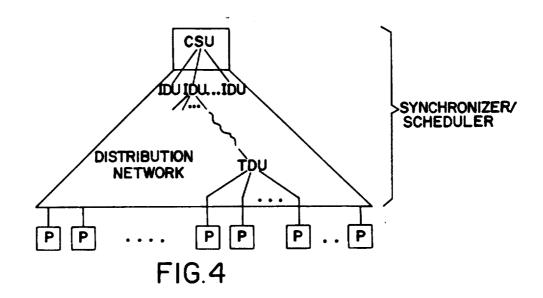

FIG. 4 is a schematic diagram of the synchronizer/scheduler apparatus architecture, featuring a central synchronization/scheduling unit and a distribution network:

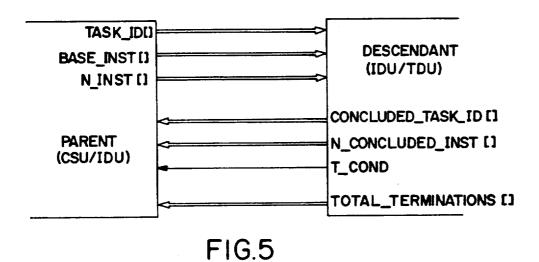

FIG. 5 is a schematic diagram of an interface through which the central synchronization/scheduling unit communicates with the distribution network of FIG. 4, and through which nodes of the distribution network communicate with each other;

FIG. 6 is a schematic diagram of an example standard input dependency structure; and

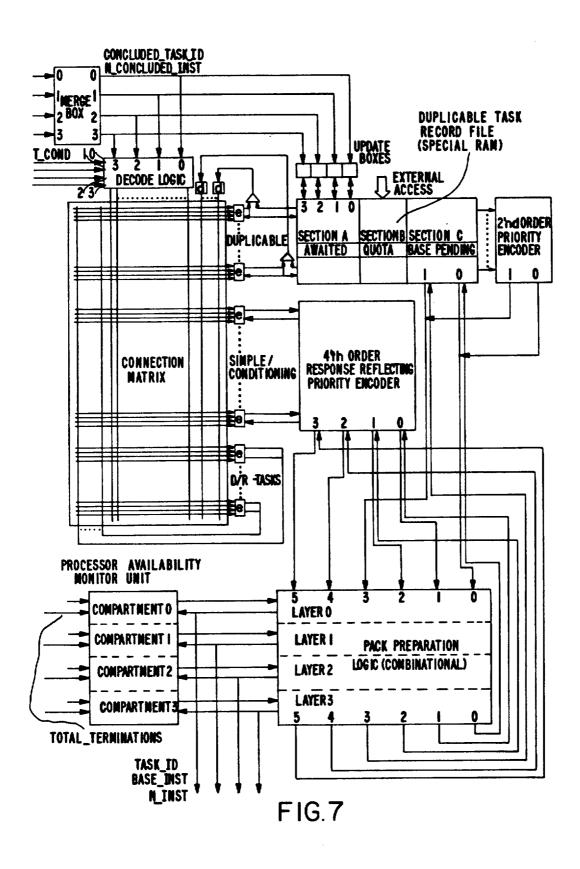

FIG. 7 is a schematic diagram architecture of a preferred embodiment of the central synchronization/scheduling unit of the invention.

### DETAILED DESCRIPTION OF A PREFERRED **EMBODIMENT**

Reference is now made to FIGS. 1-7, showing various aspects of the proposed architecture of a synchronization/scheduling subsystem for a multiprocessor. The proposed synchronizer/scheduler subsystem consists of a central scheduling unit (CSU) and an active distribution network controlling the multiple processors. The proposed subsystem is programmed with the synchronization and scheduling information for the executed parallel algorithm. The next section contains a discussion of the general system architecture, its performance and its goals. The architecture's underlying programming model is then described. Following this, the general architecture of the synchronizer/scheduler subsystem is discussed, and finally a detailed discussion of the architecture of the central unit of the subsystem is presented.

(I)

## SYSTEM ARCHITECTURE AND EXPECTED **PERFORMANCE**

A program intended for execution on a multiproces-Neumann model. They can also be compound process- 50 sor which incorporates the synchronization/scheduling scheme described herein, must be represented by a dependency graph. The dependency graph is called the program's task map; Its nodes represent tasks, and its (directed) edges represent task interdependencies. Tasks are granules of computation, of any desired size (e.g. they may embrace any number of machine instructions). The graph may contain cycles. The task map is submitted to the hardware, and used during run-time. This dependency-graph-driven mode of computation, attributed by non-elementary granularity, is referred to in the paper to Gajski et al supra as macro dataflow. Yet according to a terminology introduced by Treleaven et al, in the paper entitled "Combining Data Flow and Control Flow Computing," Computer Journal, Vol. 25 multi-threaded control flow. That is because the data communication mechanism (namely, the shared memory) is distinct here from the synchronization/schedul-

ing mechanism, and dependency arcs do not necessarily "carry data" but denote control flow.

There is a distribution between a task, which is a quantum of program code and a task map object, and a task instantiation, which is an execution process derived 5 from a task. The reason for this seemingly subtle distinction will be made clear in a later section. Until then, for the sake of simplicity, this distinction is ignored.

The multiprocessor architecture is illustrated in FIG. 1. As can be seen, the parallel operation coordination 10 subsystem (synchronizer/scheduler 10) forms an appendage to a conventional configuration of a shared-memory 12 and processors 14.

The synchronization/scheduling subsystem comprises a task map which contains dependencies between 15 tasks to be performed by the processors 14. The code of the tasks is loaded in memory, whereas the topology of the task map is held by the synchronizer/scheduler 10. The latter uses the task map for allocating tasks to processors 14. While doing so, it continuously monitors the 20 processors 14 employment state, and makes allocations dynamically and on the basis of processors availability. A task is allocated by signalling its identification information across the link 16 between the synchronizer/scheduler and the designated processor. Further param- 25 eters, or data to be processed by the task, are acquired from the shared memory 12 via link 18.

When allocated a task, a processor 14 is caused to restart, with the first instruction fetch address determined by the task's identity. The processor 14 then 30 proceeds in executing instructions fetched from main memory, until encountering an instruction signifying the end of the task. The processor 14 then enters a halted state, exporting an indication of its new state to synchronizer/scheduler 10. This indication, when re- 35 optimal load balancing by definition. ceived by synchronizer/scheduler 10, serves a twofold function: First, the processor 14 is marked free and ready for another allocation. Secondly, the event of the current task's termination is internally marked, and may cause the enabling of other tasks which depend on the 40 current one. The enabling of a dependent task takes place if all its other input dependencies have already been activated in a similar manner. (OR relations between input dependencies are also possible, and discussed further herein with regard to the architecture's 45 underlying programming model).

In addition to a task map, synchronizer/scheduler 10 is supplied with the system configuration data. This includes such details as the number of processors, the capabilities of each processor (if the processors are not 50 a-priori identical), etc.

Given a set of enabled tasks, as well as processor availability data, synchronizer/scheduler 10 then performs scheduling of those tasks. Any non-random scheduling policy must rely upon some heuristics: Even 55 when task execution times are known in advance, finding an optimal schedule for a program represented as a dependency graph is an NP-complete problem, as described in the paper entitled "NP-Complete Scheduling Problems," J. D. Ullman, J. Comput. Syst. Sci., Vol. 10, 60 June 1975, pp. 384-393. Most scheduling heuristics are bases on the critical path method, and thereby belong to the class of list scheduling policies; i.e., policies that rely on a list of fixed task priorities as described in the paper by Gransky et al supra, and the text entitled "Computer 65 and Job-Shop Scheduling and Theory," E. Coffman, Wiley Publishers, New York, 1976. List scheduling can be supported by the inventive scheme described herein,

by embedding task priorities in the task map loadmodule submitted to the synchronizer/scheduler. Whenever an allocation takes place, the allocated tasks

are those which have highest priorities amongst the

current selection of enabled tasks.

The general architectural concepts described so far may be implemented in multiple alternative ways. The processors may range from minute processing elements to large scientific processors. They are not limited to any specific type, and are not confined to the von-Neumann model. They can also be compound processing units. The architecture may also be applied to nonhomogeneous systems. The shared memory may consist of physically shared storage, possibly accessed through an interconnection network, or be distributed over the processors, as long as the common memory space is preserved, at least in part.

#### Performance Bounds

An immediate merit of the herein described scheme is that any parallel operation coordination overhead is offloaded from the processors. This activity is shifted to the special purpose hardware, and is performed in parallel with productive computation. This carries the potential for a significant shrink in overhead per synchronization point. Another merit is the optimal load balancing, attained due to the fact that allocations are performed dynamically, on a global basis, and are driven by processors availability. Optimal load balancing means that no situation can occur where enabled computational work becomes committed to a specific portion of the system which cannot accomodate it at that moment, while a processor not belonging to that portion is idling. It is clear that the conditions specified above ensure

Synchronization rate is measured here as the total flow-rate of task initiation (namely, synchronization flow-rate) across the synchronizer/scheduler's ports. If the synchronizer/scheduler provides too low a synchronization flow-rate, a synchronization bottleneck may result. In considering the question of whether the synchronizer/scheduler's flow-rate capability constitutes a bottleneck in comparison to the requirements of the parallel program, the graph of FIG. 2 may be used.

The horizontal axis depicts the given maximal flowrate of synchronizer/scheduler apparatus 10, scaled in terms of a measure which is called the canonical flowrate, or fc, which is a parameter of the program being executed, and is the only such parameter involved in the analysis. It is defined as the average flow-rate developed when the program is run on a system containing an infinite number of processors and an ideal synchronizer/scheduler 10 apparatus, one having infinite flow-rae capability. An equivalent definition would be the ratio between the total number of task executions that must occur, and the length of the critical path on the program's task map. In the ideal execution process, the momentary flow-rate may sharply deviate from the average fc.

The vertical axis of the graph of FIG. 2 depicts the overall slowdown in program execution, incurred by the given limitation on the synchronizer/scheduler's flow-rate, still under the assumption that the number of processors is unlimited. This assumption established a "worst-case" condition; its relaxation implies a potential decrease in the demand for flow-rate. A lower bound and an upper bound on slowdown are depicted. The lower bound reflects the fact that the time needed to

Q

D-tasks serve to express non-standard input dependency schemes and to manipulate dependency structures.

FIG. 3d shows reset tasks, noted as R-tasks which,

10

complete the execution for a program can be not shorter than the minimal time needed for allocating all of its tasks. The lower bound is valid for any synchronization/scheduling mechanism whatsoever, whether based upon hardware or upon software. The upper bound is 5 valid only under the assumption that the processors are relieved from any synchronization/scheduling-related overhead activity, as happens in this invention. The upper bound can be proven mathematically, based on the assumption that the flow-rate is only semi-finite, in 10 the sense of having only one direction of limitation. The mathematical proof and rationale for this assumption are included in the material by N. Bayer entitled, "A Hardware-Synchronized/Scheduled Multiprocessor Model," submitted as a M. Sc. Thesis, EE Department, 15 Technion, Israel Institute of Technology, January 1989 (as yet unpublished).

In order to sustain high flow-rate, it is also important to attain low enabling latency. This parameter reflects the time which elapses from the termination of the last task which prohibits the enabling of another task, until the latter can be allocated. Low enabling latency is desirable in order to allow efficient parallelism even in the more difficult and challenging cases, when the program's degree of parallelism is roughly the same as the number of processors, i.e. when there is no large reservoir of enabled tasks.

(II)

## THE UNDERLYING PROGRAMMING MODEL 30

The programming model is the collection of rules and options serving for the construction of task maps, which is directly supported by the hardware. A task map coded according to this programming model will closely correspond to the load-module submitted to the 35 synchronizer/scheduler. Preparation of the ultimate load-module will not include any essential transformation of the program.

This layer may serve as the basis for the definition of higher layers. Tools such as compilers and macro-40 expanders can be developed, which accept more powerful and abstract software constructs and translate them into task maps of the kind directly supported by the hardware

Consolidation of the programming model includes 45 software aspect related considerations, associated with an assessment of its computational power vs. the hardware investment needed. In the following description, the details of the programming model for the high flow-rate synchronizer/scheduler architecture are presented 50 by review of the programming features which are illustrated by graphic notations shown in FIG. 3.

FIG. 3a shows the AND/OR relations between task input dependencies, with the standard task input dependency mechanism implementing a product-of-sums 55 logic. Arrows entering a task symbol denote AND related dependencies, in accordance with the common notation convention for dependency graphs. Arrows approaching a task symbol via a circle sign denote OR related dependencies.

FIG. 3b shows pre-enabled task notation, with each program task being initialized as enable or non-enabled. Those initialized as enable are called pre-enable, and must be specifically declared so.

FIG. 3c shows dummy (or degenerated) tasks, noted 65 as D-tasks, which when enabled, are not subjected to allocation; instead they are immediately declared as terminated, internally to the synchronizer/scheduler.

FIG. 3d shows reset tasks, noted as R-tasks which, similar to D-tasks, are also treated internally within the synchronizer/scheduler. However, an R-task does have an execution body: It rests all input dependencies of the tasks governed by it to a non-active state. It is useful for purging of "control tokens."

FIG. 3e shows conditioning tasks, which is the mechanism underlying global conditioning (task-local conditioning is implemented using the processor's branching instructions). The global conditioning mechanism is based upon a scalar boolean value, named termination condition (t\_cond), which is returned to the synchronizer/scheduler upon the termination of each task. When a task begins, its t\_cond is automatically initialized to a "1" value. The task is allowed access to the t\_cond as a variable, and rests it to "0".

If a task is denoted  $t_0$ , each output dependency of  $t_0$  may be of type " $\phi$ ", "0" or "1". Dependencies of types "0" and "1" are activated upon termination of  $t_0$  only in conjunction with the appropriate t—cond value. A task having at least one non-" $\phi$ " output dependency is termed a conditioning task, and must be explicitly declared so. The " $\phi$ " signs are omitted in the graphic notation from output dependencies not belonging to conditioning tasks.

FIG. 3f shows duplicable tasks, which constitute a mechanism for supporting a particular form of dynamic process generation. Let <task\_id> be a duplicate task. The enabling of <task\_id> generates <inst\_quota> instantiations pending for allocation. Execution of these instantiations is in SPMD style, as described in the paper "Programming for Parallelism", A. H. Karp, IEEE Computer, Vol. 20 No. 5, May 1987, pp. 43-57. All processors receiving an instantiation of <task\_id> execute the same code, by under the modification of the instance number transmitted by the synchronizer/scheduler. The event of <task\_id>'s termination is identified with the termination of its last instantiation. The number of instantiations <inst\_quota> is initialized at compile-time, but may be updated at run-time by the processors. For this purpose, the internal register within the synchronizer/scheduler dedicated to <task\_id> is subject to external access (write only), as if it were a global memory cell. A duplicate task cannot be a conditioning one.

The introduction of duplicable tasks necessitates the following refinements in terminology: the term "computational task" refers to pieces of computational work in general. However, in the context of this embodiment, computational tasks performed by the processor are referred to a "task instantiations" or briefly, instantiations, while the term "task" is reserved for the task-met objects themselves.

(III)

## GENERAL ARCHITECTURE OF THE SYNCHRONIZER/SCHEDULER

FIG. 4 illustrates the synchronizer/scheduler apparatus architecture. It is divided into two modules: A central synchronization/scheduling unit (CSU) and a distribution network. The distribution network mediates between the CSU, which constitutes the heart of the synchronizer/scheduler, and the processors. Its function is not the mere passive data transfer, but as further

described herein, it creates an effect of amplifying the synchronizer/scheduler apparatus 10 flow-rate, in comparison with the flow-rate of the CSU alone. As this distribution network shares some common features with combining networks for shared memory access as described in the paper to Gottlieb et al supra, they will compared at the end of this section.

While the internal implementation of the CSU constitutes the theme of the next section, this section discusses the architecture and operation of the synchronizer/- 10 flow-rate capacity may not be fully utilized. scheduler as a whole.

The proposed structure is founded upon the inclusion of duplicable tasks in the programming model. The existence of duplicable tasks in a program helps make number of task-instantiations allocated to processors (the enabling of a duplicable task is considered a single enabling). Thus, the average rate of task enablings, denoted fo is liable to be smaller than the flow-rate of allocating task-instantiations to processors, denoted fa. 20 The ratio  $f_r = f_a/f_e$  is equal to the average number of instantiations per task (the average calculation includes also the regular tasks, which release exactly one instantiation per enabling, but does not include D-tasks and R-tasks). The factor f, which is a property of the pro- 25 gram in combination with its input, is likely to reach orders of magnitude of tens, hundreds, or even more, as indicated by benchmark examples. Examples: instantiation quotas of duplicate tasks correspond to the sizes of blocks within the complete matrix; in particle-system 30 simulation programs, the instantiation quotas of duplicable tasks may correspond to the number of interaction/maintaining particle pairs.

The interface between the distribution network and the processors carries individual allocation and termina- 35 tion messages, whereas the interface between the CSU and the distribution network carries allocation packs and termination packs. A pack contains one instantiation or more out of the collection of instantiations released by a single task-enabling. If the pack contains all 40 the instantiations which were released, it is called a complete pack; otherwise it is called a partial pack. The instantiation indices belonging to an allocation pack must form a continuous sequence. The coding of packs employ a certain form of compression, such that the 45 lar in the communications capacity. coding format employs a fixed number of bits: The task's identity is always coded; in an allocation pack the sequence of indices is also coded, e.g. as a pair, incorporating the first index and the sequence length. In a tertance, and only their quantity is coded. For the purpose of discussing communications flow-rates, and due to this manner of coding, packs and individual messages will be counted according to the same measuring-rod.

The task map is concentrated in the CSU, which 55 monitors the enabling of tasks. Allocation packs sent by the CSU are decomposed during their passage through the distribution network, and delivered to the processors as individual instantiations. The opposite operation, termed herein merge, is performed on termination mes- 60 sages. In this way, the communications flow-rate between the processors and distribution network may be amplified in comparison to the flow-rate of communications between the distribution network and the CSU. Namely,  $f_{csu} < f_a$  where  $f_{csu}$  denotes the total communi- 65 cations flow-rate across the CSU interfaces.

It should be noted that f<sub>csu</sub> is not always the same as fe. Consider operating conditions where the collection of processors functions as a sink, i.e. it is willing to absorb any instantiation of any enabled task immediately, and there is a large reservoir of enabled tasks which is steadily reproduced. Under such a situation, the CSU sends and receives complete packs exclusively, and therefore its communications flow-rate is congruent to the enabling rate, namely  $f_e = f_{csu}$ , and the condition  $f_a = f_r \times f_{csu\ max}$  holes. Under different operating conditions, the CSU may send and receive partial packs, or its

### Structure of the distribution network and types of interfaces

The distribution network is modular, as it consists of the total number of task enablings lower than the total 15 basic building blocks from which a desired configuration may be assembled. It is also possible to introduce local modifications and extensions without total dismantling and reassembly. As shown in FIG. 4, the building blocks are termed distribution units and are of two kinds: Terminal distribution units (TDU's) and Intermediate Distribution units (IDU's). The distribution network has a forest topology, complemented by the CSU into a tree, with the CSU at its root. It is reasonable to assemble balanced or almost balanced tree configurations, although any other tree may be assembled as well. The tree leaves are TDU's, and the processors attach to them; the internal nodes are IDU's. An extended tree is defined as one having leaves which are the processors themselves. Let v be a non-leaf node of the extended tree. The number of ports through which descendant nodes can be attached to v is designated as v's fan out. All interfaces on individual ports are of one of the following two types:

$$[parent = CSU/IDU] - [descedant = IDU/TDU]$$

(1)

$$[parent = TDU] - [descendant = P]$$

(2)

The major difference between interface types is that (1) is intended for transferring packs, whereas (2) is intended for transferring messages on individual or terminated instantiations. All units of the same kind constitute identical exemplars. Also, all interfaces of the same type are identical in every respect and in particu-

## Organization of the Configuration and Processor Employment Data

In contrast to the task map, the configuration data are mination pack, the instantiation indices have no impor- 50 distributed across the whole of synchronizer/scheduler apparatus 10. Each synchronizer/scheduler unit keeps the summation of configuration data pertaining to each sub-tree connected to any of its descendant ports. The information concerning current processor employment is also distributed in the same manner. For example, in a homogeneous system, the total number of disengaged processors belonging to a certain sub-tree is maintained, instead of separate information for each processor. For a TDU, a "Sub-tree" is always identical to a single processor. The update of processor employment data is performed in a distributed fashion: Each unit updates its own data, according to the amount of allocations and terminations passing through it.

Let v be a distribution unit. The configuration and processor employment data for the sub-tree with v at its root is maintained by v's parent. Therefore, it is guaranteed that the allocations v receives are within the limits of the current sinking ability of that sub-tree. According

to the configuration and processor employment data maintained by v itself, it must divide these allocations among its descendants. Suppose there are multiple division possibilities, and the system is symmetrical. The allocations may then be randomly divided.

However, the simplest way for dividing the allocations is according to fixed port priorities. Determination of the descendant port priorities at each unit induces global priorities for the external ports of the synchronizer/scheduler. These global priorities can be 10 exploited for establishing balanced allocation when each processor is built to accomodate up to two contexts, and is connected to the synchronizer/scheduler via two separate ports. Every processor is then assigned a high priority and a low priority port. This outline may 15 be generalized also for more than two ports. The motivation for supporting multiple contexts within a processor is concerned with countering memory latency, as discussed in the reference by N. Bayer, supra.

## Management of Termination Information

The termination messages generated by the processors serve two distinct functions:

- a) Enabling of new tasks dependent on the terminated

- b) Monitoring processor employment state.

These two functions induce conflicting considerations regarding the policy of termination packs forwarding through the distribution network:

For serving function (a) well, fragment packs need 30 not be hurriedly sent towards the root of the tree. Since the termination of a duplicable task is defined as the termination of all of its instantiations, such fragments may be held up at the distribution network nodes in order to achieve maximal unification. This unification is 35 indispensable for the reduction of the amount of information traffic at levels closer to the root of the tree.

Contrarily, function (b) calls for a policy of transferring every termination message without any delay. This can be illustrated by considering an extreme case: Sup- 40 pose that there are 256 processors, which have received exactly 256 instantiations of the task  $t_x$  concurrently. While 255 instantiations require T computation time, one instantiation requires 100×T computation time. In waiting for a full unification of the termination pack, 45 the assembled configuration, and does not depend on 255 processors are disutilized for duration of 99\*T.

The proposed solution for this problem is a split into two separate mechanisms, each of them handling one of the functions. A distribution unit v receives two kinds of data from its descendants:

- (1) Termination packs, as described above (not to be exploited as an information regarding processors disengagement).

- (2) Messages expressing qualities of processors which have entered a halted state (disregarding the tasks 55 conducted by them).

Under the implementation presented in the following section, each of these kinds of data is transferred on its own dedicated wires.

Upon receiving a datum of kind (1) relating to a task 60 tx, v accumulates it into its count of tx's terminated instantiations; Yet nothing is sent to v's parent, unless this datum completes the count to the total sum of tx's allocations previously passed through v. When the termination data regarding t<sub>x</sub> is sent to v's parent, the 65 above-mentioned counts are reset, so the maximal value of these counts if bounded by the maximal amount of instantiations a task is allowed to have for one enabling.

14

Hence the number of termination packs submitted by v to its parent until a certain moment, is less than or equal to the number of allocation packs received by v until that moment. (An inequality relation may hold not only due to unfinished instantiations, but also due to coverage of several allocation packs by a single termination pack). Thus, the mean demand for communications traffic of termination packs at every point within the network is equal or less than the traffic of allocation

Contrarily, data of type (2) arriving at v from several descendants concurrently are merged into a unified datum, which is sent to v's parent immediately (in addition to using them for internal update at v). The possibility of always performing such a merge stems from the way employment data are organized. Due to this regular merging possibility, any delays associated with waiting for available communication paths (for type (2) data) are eliminated. The event of a processor belonging to v's sub-tree becoming available, will be reflected at the employment data maintained by v within a delay proportional to the length of the path between the processor and v.

## Characterizing Parameters

The parameters characterizing a specific synchronizer/scheduler can now be summarized:

Loading Capacity:

The maximal size of a task map which can be loaded. This parameter is expressed in terms of quantity of tasks, and/or in terms of quantity of dependency con-

## Reduced Maximal Flow-Rate:

Maximal synchronization flow-rate which can be attained for programs which do not include duplicable tasks. This parameter actually expresses the CSU flowrate, and is independent of the assembled configuration. The reduced maximal flow-rate is equal to a type (1) interface's communications capacity, times the fan-out of the CSU.

## Extended Maximal Flow Rate:

Maximal synchronization flow-rate which can be attained for any program. This parameter depends on the CSU's fan-out. The extended maximal flow-rate is equal to a type (2) interface's communications capacity, times the total number of TDU's descendant ports.

Enabling Latency:

Duration from the moment a processor P<sub>1</sub> announces the termination of an instantiation belonging to a task t<sub>1</sub> until a processor P<sub>j</sub> receives an instantiation of a task t<sub>j</sub> depending on t<sub>1</sub>, provided:

- a) The termination and allocation messages involved are not delayed due to contention on communication paths.

- b) No other terminations are needed to trigger t/s enabling. The synchronizer/scheduler's enabling latency is composed of the CSU's enabling latency, plus a component proportional to the depth of the distribution network tree. This second component depends upon fan-out values, and upon the assembled configuration. When the tree is balanced, this component is logarithmic in the number of synchronizer/scheduler ports. Note that the enabling latency may be more complex than a fixed, single-valued parame-

Allocation Advances:

the canonical flow-rate, whereas in the latter case the total number of released instantiations is taken into the analysis.

16

Quotas for over-allocations of task instantiations, which the CSU or every IDU separately (but excluding the TDU's) are programmed to allocate their descendants, beyond the calculation of free processors. Allocation advances are aimed at compensating against the 5 delays associated with the flow of processor disengagement information through the network. Implementation of allocation advances obliges that the distribution units have a capability of storing buffered allocation packs. This is a set of programmable parameters. There is 10 presented herein the principal possibility of using allocation advances, but not the computation of their optimal values. Although allocations to individual processors are still made on the basis of availability, the optimal load balancing, as defined previously regarding 15 System Architecture may be disrupted, and this should be assessed quantitatively. When the program's degree of parallelism is sufficiently higher than the number of processors, so there is a sufficient reservoir of enabled tasks, allocation advances can be set so as to saturate the 20 distribution network with ready-to-execute task instantiations. Under such a situation, a processor is allocated a new task instantiation immediately as it terminates the previous one, avoiding any overhead-idling whatso-

The fact that the task map is totally concentrated in the CSU facilitates the possibility of allocating any task instantiation to any processor, and establishes the capability of dynamic regulation of allocations (distribution of the task map is possible in hierarchical extensions of 30 the general scheme discussed here). However, because of this same fact, the CSU induces a certain extent of centralization in the system; from here stems the importance of amplifying its flow-rate through the distribution network.

Assuming the CSU cost is not dominant, then relatively small configurations, assembled around a given CSU module while rendering its flow-rate superfluous, can still be cost-effective.

The configuration and processor employment data 40 maintained for each descendant port by a TDU, are reduced in comparison to the data maintained by an IDU. In addition, a type (2) interface is reduced in comparison to a type (1) interface. Therefore, for an identical cost, a TDU's fan-out is anticipated to be higher 45 than an IDU's fan-out. An even higher fan-out can be attained for a TDU through a variation of the basic structure, based on another consideration: Execution of a task instantiation by a processor lasts a certain duration, and time intervals do exist during which no communications between a given processor and the TDU takes place. On the account of this unused communications capacity, a group of processors can be attached to a single port in a bus configuration.

Under the architecture described thus far, all external parts of the synchronizer/scheduler can be driven simultaneously, hence (assuming that every processor has its private port) the extended maximal flow-rate immanently matches the maximal sinking capability of the processors. As far as flow-rates are concerned (namely, 60 disregarding latencies), the only possible source for a bottleneck is the reduced maximal flow-rate; that is, the CSU flow-rate. The bounds on slowdown due to a limited flow-rate presented earlier regarding FIG. 2 apply to the CSU flow-rate in the same way they apply 65 to the flow-rate of the synchronizer/scheduler as a whole. The only difference is that in the former case the total number of enablings is taken into the calculation of

## Comparison with the Combining Network

The conjunctive feature of both the distribution network and the combining network for memory access proposed in the paper by Gottlieb et al supra, is the decomposition and unification of information performed at every network node. The differences between the networks stem from the fact that they are destined to attach to inherently different units, in that end which is not attached to the processors.

There is a difference in topology, which is also a difference in complexity: The combining network has been proposed in an N $\times$ N Omega topology, typically consisting of  $2\times2$  elements; the distribution network has an N $\times1$  tree topology, consisting of (fan-out) $\times1$  elements.

In order to isolate further differences, consider a combining network for memory access which is based on a tree topology as well. (This is possible when all synchronization data are concentrated in a single memory module). In the distribution network the active agent is situated at the root of the tree (the CSU), and the passive agent is situated at the leaves (the processors). The opposite is true regarding the combining network: The active agent is situated at the leaves (the processors), and the passive agent is situated at the root (the memory module). This fact generates differences in the mechanisms of information flow.

Information transmitted from the root of the tree in the combining network is destined for pre-determined addresses (addresses of specific processors). Contrarily, in the distribution network addresses are established during the passage through the network, in a distributed process that has to do with load regulation. In the direction from the leaves to the root, the merging of information in the combining network is performed on an occasional basis: A merge takes place only if two mergeable items occur at the same node at the same time. In the distribution network, however, there are rules to enforce the merge of items, regardless of arrival times and at the level as far as possible from the root of the tree.

The following duality exists between the two networks: In the combining network, decomposition of data is dictated by their merge (the subject for decomposition are responses returning from memory); In contrast, in the distribution network the merge of data is dictated by their decomposition (the subject for merge are termination messages returning from the processors). However, the mechanism controlling the sending of information on the direction from the root to the leaves in the distribution network, seems to be essentially different than the mechanism controlling the sending of information on the direction from the leaves to the root in the combining network.

### (IV)

# STRUCTURE OF THE CENTRAL SYNCHRONIZATION/SCHEDULING UNIT

The internal architecture of the CSU is now presented. As noted in the previous section, this unit is the only possible source for a performance limitation as far as flow-rates are concerned. Therefore, it is the most important among the synchronizer/scheduler units. The CSU holds the task map, and is responsible for the

function of detecting/monitoring of task enablings. In addition, the CSU keeps its own configuration and availability data, and performs a distribution function, in an essentially similar manner to a distribution network node. Hence, the CSU is the most complex of all syn- 5 chronizer/scheduler units, and apart from playing its own singular role, it plays a representative role with regard to the embodiment of the whole apparatus. The design space is rich with possibilities and an optimal design may be achieved with additional work. The 10 design version presented herein achieves some desired properties related with flow-rate and enabling latency, and represents a certain archetypical outline; Yet simplicity considerations play a substantial role in this version. Throughout the course of presentation, potential 15 improvements, as well as alternative design options, are pointed out.

In order to eliminate any ambiguity, the abstraction levels that are dealt with in the context of presenting the CSU architecture, reach the level of logic design.

The timing discipline that appears to be most appro-

large, space-distributed system; b) preventing excessive mutual coercion of operational rates among units, in order to increase utilizations and decrease delays. Nevertheless, the design presented herein is based on the discipline of synchronous timing with a single clock, due to its simplicity. Under this timing discipline each signal line assumes a single valid value on each clock cycle, which is the value that stabilizes towards the end

of the cycle.

In the following design version, the system is assumed to be totally symmetrical, so that any processor may receive any task, and without any preferability differences between processors.

## Definition of Type (1) Interface

The CSU communicates with the distribution network through type (1) interfaces (as denoted in the previous section). The lines that take part in a type (1) interface are graphically summarized in FIG. 5, and the duties of the various lines are specified in the following table.

### TABLE I

|                      | I ADLE I                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Line/<br>Line Group  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TASK_ID[]            | Identification number of the task to which the current alloca-<br>tion pack pertains. (A mapping from this identification<br>number to the address of the task's code in main memory is<br>accomplished through fast tables coupled to the processors.<br>The address is not transmitted directly, in order to make<br>economical usage of lines).                                                                                                                             |

| BASE_INST[]          | Number of the least instantiation among the sequence of instance numbers belonging to the current allocation pack. (If the identification number TASK_ID[] pertains to a task which has not been declared as duplicable, then the contents of the BASE_INST lines are meaningless for the current clock cycle).                                                                                                                                                                |

| n_inst[]             | Amount of instantiations contained in the current allocation pack. (If no allocation pack is transferred on the current clock cycle, a zero value appears on this time group, and random values appear on the TASK_ID[] and BASE_INST[] line groups. In case that the task is non-duplicable, as in the case that the pack contains a single instantiation of a duplicable task, a value of 1 appears on the N_INST[] lines).                                                  |

| CONCLUDED_TASK_ID[]  | Identification number of the task to which the current termination pack pertains.                                                                                                                                                                                                                                                                                                                                                                                              |

| N_CONCLUDED_INST[]   | Amount of instantiations contained in the current termination pack. (If no termination pack is transferred on the current clock cycle, a zero value appears on this line group, and random values appear on the CONCLUDED_TASK_ID[] and T_COND[] lines. In case that the task is non-duplicable, as in the case that the pack contains a termination message pertaining to a single instantiation of a duplicable task, a value of I appears on the N_CONCLUDED_INST[] lines). |

| T_COND               | Termination condition value pertaining to the current termination message. (If the task's identification number, CONCLUDED_TASK_ID[], does not belong to a conditioning task — this line has a meaningless contents on the current clock cycle. In particular, the T_COND is meaningless when the contents of the N_CONCLUDED_INST[] lines are greater than 1).                                                                                                                |

| TOTAL_TERMINATIONS[] |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

priate for the synchronizer/scheduler (as well as for other parts of a multiprocessor, at certain levels of the structural hierarchy) is self-timing, as described by C. L. Seitz in the text entitled "Introduction to VLSI Systems", C. Mead et al, Addison-Wesley, 1980, chap. 7 pp. 218-254. The reasons for this are: a) the difficulties associated with spreading of clock signals throughout a

## General Characteristics

In the current CSU design version, a high flow-rate and low enabling latency is preferred to high loading capacity. (Benchmark examples indicate that a loading capacity of the order of several tens of tasks is at the

18

edge of acceptability; a duplicable task is considered as a single task for the sake of capacity calculation).

The internal representation of a task map within the CSU in this version is not through memory cells, but rather through a programmable topology of connec- 5 tions (logical "short circuits") between lines. This implementation approach may be entitled as connectionist approach, due to its affinity to connectionist architectures, as described in the paper entitled "Connectionist Architectures for Artificial Intelligence", S. E. Fahl- 10 man et al, IEEE Computer, Vol. 20 No. 19, Man. 1987, pp. 100-109. Yet another implementation approach may rely on associative memory: The memory will be organized in a way that each program dependency will be allocated a memory word, where the identification 15 number of the task to whom it is an output dependency will serve as an access key, and the identification number of the task to whom it's an input dependency will serve as the datum to be fetched.

In the current version, the CSU does not contain a 20 central controller designed on the basis of a state diagram, and there is no division into a control unit and a data path. The architecture is founded upon wide parallelism amongst a broad collection of simple elements. The following parameters are now defined:

$\lambda_1$  = the CSU's fan-out.  $\lambda_1$  equals the maximal amount of allocation packs (and termination packs) that can be transferred by the CSU on a single clock cycle.

$\lambda_2$ =maximal amount of distinct TASK\_ID values belonging to duplicable tasks which can appear on the 30 CSU interfaces on a single clock cycle  $(\lambda_2 \leq \lambda_1)$ .

$\lambda_3$  = maximal amount of non-duplicable tasks which can be allocated by the CSU on a single clock cycle  $(\lambda_3 \leq \lambda_1)$ .

This version's underlying fundamental outline allows 35 any combination of  $\lambda_1$ ,  $\lambda_2$  and  $\lambda_3$ . The concrete design presented here embodies  $\lambda_1=4$ ,  $\lambda_2=2$ , and  $\lambda_3=4$ .

An approximate form of list scheduling is supported: On every clock cycle the  $\lambda_2$  (at the outside) most prior duplicable tasks are selected, and also, separately, the 40 λ<sub>3</sub> (at the outside) most prior non-duplicable tasks. This collection of  $\lambda_2 + \lambda_3$  tasks (at the outside) is also subordinated to a priority setup, according to which  $\lambda_1$  (at the outside) allocation packs are produced. In the concrete design presented here,  $\lambda_2 + \lambda_3 = 6$  holds, and the scale of 45 6 priorities is as follows: The upper two priorities are granted to the two most prior non-duplicable tasks; then comes the most prior duplicable task; then the remaining two non-duplicable tasks, and eventually the remaining duplicable task. This is an example, but any 50 other priority setup might be chosen. The policy in allocating a duplicable task in this version is to allocate maximum of its instantiations, and therefore up to  $\lambda_1$ packs pertaining to the same duplicable task may be generated on a single clock cycle.

The tasks' priorities are mapped into their internal addresses within the CSU, and these are identified with the TASK\_ID values taking part in transactions between the CSU and the outside world. In this version, guishes a task which has been declared as duplicable from a task which has not been declared so. Among two tasks having the same most significant bit, the one whose other TASK\_ID bits determine a higher numerical value is the more prior.

The loading capacity is given in the general outline represented by this version as a set of several parameters:

- A) Separate values for the capacities of duplicable tasks, of conditioning tasks, of regular (simple) tasks, and of D-tasks/R-tasks. (The capacities of duplicable and conditioning tasks can be exploited for regular tasks

- B) The available standard dependency structures, corresponding to various sections of the task capacity. In the concrete design presented here, all tasks of all kinds have the standard input dependency structure depicted in FIG. 6. Also, in this design every task may be governed by one R-task at most.

Arbitrary dependency constructs can be created by partial utilization of standard structures on the one hand, and by usage of D-tasks on the other hand. In the embodiment of the central synchronization/scheduling unit (CSU) described, any desired standard input dependency structure can be supported.

## Enabling latency specifications of the CSU

Let  $t_x \rightarrow t_y$  be a dependency, forming the last input dependency to prohibit the enabling of ty at certain execution circumstances. Suppose that under these circumstances there is no delay in ty's allocation (or in the allocation of its first pack) due to unavailability of a free interface or free processors. Let i be the clock cycle whereon tx's termination message (or tx's last termination pack) has appeared. Then the clock cycle wheren ty will be allocated by the CSU (or its first allocation pack will be exported) is given by the following table:

TABLE II

| t <sub>p</sub> /t <sub>x</sub> | non-<br>duplicable | duplicable |

|--------------------------------|--------------------|------------|

| non-<br>duplicable             | i + 1              | i + 2      |

| duplicable                     | i + 2              | i + 3      |

There is room for improvement of this version by introducing more intensive pipelining. This has been avoided to preserve simplicity considerations. Introduction of more intensive pipelining may facilitate for raising the clock frequency, that is to say raising the flowrate, but may increase the enabling latency in terms of clock cycles.

## **Detailed Structural Description**

The main drawing of the CSU design is given in FIG. 7. Some of these functional modules are considered to be general building blocks. Still others are specific CSU modules, which functionality is described in here, while their internal structures are illustrated in the appendix. The bold lines in FIG. 7 depict line groups or clusters of line groups, while the regular lines in the figure depict scalar (single bit) signal lines. In order to avoid overloading, signal names are not indicated on the drawing, apart from the names of the external lines which belong to interface number 0. The names can be inferred from the verbal descriptions.

The main drawing does not depict the mechanisms the most significant bit (msb) of the TASK\_ID distin- 60 serving at task map load-time, but only the mechanisms serving during run-time. Also, the clock signal lines, entering all modules which do not constitute combinational logic, are omitted. Apart from the interfaces between the CSU and the distribution network, there is an additional external interface of the CSU, through which this unit is deemed as a memory module (write only). This interface serves the update of duplicate tasks instantiation quotas during run-time. The interface is

shown in the drawing, but the hardware mechanisms associated with it are not detailed.

The connection matrix and the array of enabling cells (e-cells) constitute the heart of the CSU. Loading of a task map involves editing the connections in the matrix. 5 The matrix columns are maped onto TASK\_ID's that appear on the external interfaces, and so are the enabling cells. Therefore the determination of the TAS-K\_ID's of the program tasks (following priority considerations) creates a mapping between them and en- 10 abling cells and connection matrix columns. A column of the connection matrix is stimulated (driven to logical "1" for one cycle exactly) following the termination of the corresponding task. Therefore, to a column which is mapped to some task tx, there will be connected rows 15 belong to enabling cells which are mapped to tasks that depend on tx. For a given enabling cell, the row to be connected is selected according to the particular dependency pattern.

The detection of an event where a task becomes al- 20 lowed for execution, namely, the enabling of a task, is manifested in setting (turning on) the enabling cell which is mapped to it; namely, in the entering of the cell into a state wherein its Q output is driven to a logical "1".

If an enabling cell belongs to the group which is intended for mapping to D-tasks/R-tasks, its setting causes the stimulation of the R input of that same cell, as well as the stimulation of the connection matrix column mapped to that same task. That is to say, all the output 30 dependencies are activated, and the cell itself is reset on the successive clock cycle. Reset of dependencies, defined when the cell serves an R-task, also takes place on the successive clock cycle, due to stimulation of r type rows connected to that column. (The following con- 35 straint is obeyed; Any task depending on an R-task must not be allocated before the reset of dependencies is completed).