# THE INTERACTION BETWEEN WORKLOADS AND ARCHITECTURE IN HIGHLY-PARALLEL CHIP MULTI-PROCESSORS

Oved Izchak

# THE INTERACTION BETWEEN WORKLOADS AND ARCHITECTURE IN HIGHLY-PARALLEL CHIP MULTI-PROCESSORS

**Research Thesis**

In Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering

### Oved Izchak

Submitted to the Senate of the Technion – Israel Institute of Technology

Tamuz 5773

Haifa

June 2013

# Acknowledgements

The research thesis was done under the supervision of Prof. Uri C. Weiser, Prof. Idit Keidar, and Prof. Avinoam Kolodny, in the Faculty of Electrical Engineering.

I am deeply grateful to my three advisors for their wise guidance, inspiration, passion and patience. My appreciation for your care and support for my education and growth cannot be overstated; thank you.

I thank Dr. Zvika Guz for introducing me to this area of research and for his collaboration and contribution to this work.

I thank Prof. Ran Ginosar and Prof. Avi Mendelson for their insights and valuable advice.

I thank Yaniv Ben-Yitzhak for his collaboration and illuminating discussions, in particular about architecture aspects close to the scope of this work and beyond it, which greatly improved my perspective and understanding.

Last but not least, I thank my colleagues in Prof. Idit Keidar's research group: Liat Atzmon-Guz, Ittay Eyal, Dmitri Perelman, Dmitry Basin, Nathaniel Azuelos, Elad Gidron, Eyal Zohar, Mark Silberstein and Stacy Patterson. Collaborating and having discussions with you was pure joy.

# **Table of Content**

| Abstract    |                                                    | 1 |

|-------------|----------------------------------------------------|---|

| Abbreviatio | ons                                                | 3 |

| Chapter 1.  | Introduction                                       | 5 |

| 1.1. Re     | esearch overview                                   | 5 |

| 1.2. Su     | mmary of Contributions                             | 6 |

| 1.3. Re     | esearch Method                                     | 7 |

| Chapter 2.  | Many-core Architecture Model                       | 9 |

| 2.1. Sy     | stem Model                                         | 9 |

| 2.2. Ar     | nalytical Model 1                                  | 1 |

| 2.3. Si     | mulation Model 1                                   | 3 |

| Chapter 3.  | The Simulator 1                                    | 5 |

| 3.1. Ba     | sic requirements 1                                 | 5 |

| 3.2. Ar     | chitecture                                         | 7 |

| 3.2.1       | I. Functional execution scheduling1                | 7 |

| 3.2.2       | 2. Inter-thread communication effects preservation | 0 |

| 3.2.3       | 3. Achieving execution-driven simulation 2         | 2 |

| 3.3. Im     | plementation                                       | 2 |

| 3.3.1       | 1. Reducing context switches 2                     | 2 |

| 3.3.2       | 2. Timing model execution thread 2                 | 5 |

| 3.3.3       | 3. Limiting the size of a segment                  | 8 |

| 3.3.4       | 4. Simulated architecture software scheduling      | 9 |

| 3.4. Su     | mmary                                              | 0 |

| Chapter 4. Benchmarks parallelism scalability study | 31 |

|-----------------------------------------------------|----|

| 4.1. Introduction                                   | 31 |

| 4.2. Measurement methodology                        | 35 |

| 4.3. Simulation results                             | 38 |

| 4.3.1. blackscholes                                 | 38 |

| 4.3.2. bodytrack                                    | 39 |

| 4.3.3. canneal                                      | 42 |

| 4.3.4. dedup                                        | 45 |

| 4.3.5. facesim                                      | 49 |

| 4.3.6. ferret                                       | 52 |

| 4.3.7. fluidanimate                                 | 55 |

| 4.3.8. raytrace                                     | 58 |

| 4.3.9. streamcluster                                | 61 |

| 4.3.10. swaptions                                   | 64 |

| 4.3.11. vips                                        | 67 |

| 4.3.12. x264                                        | 70 |

| 4.3.13. freqmine                                    | 73 |

| 4.4. Conclusions                                    | 74 |

| Chapter 5. Cache analytical modeling study          | 77 |

| 5.1. Introduction                                   | 77 |

| 5.2. Methodology                                    | 78 |

| 5.3. Simulation results                             | 81 |

| 5.3.1. Blackscholes                                 | 81 |

| 5.3.2. Bodytrack                                    | 84 |

| References                       |     |

|----------------------------------|-----|

| Appendix: simulation environment | 115 |

| Chapter 6. Summary               | 113 |

| 5.4. Conclusions                 | 111 |

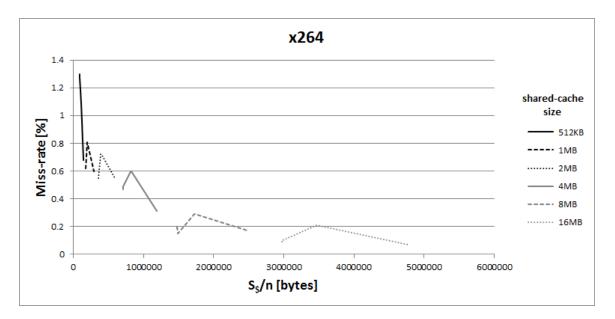

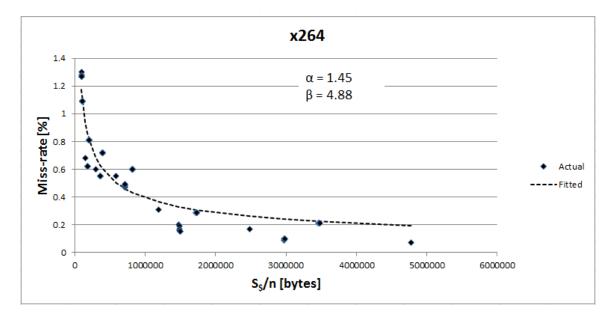

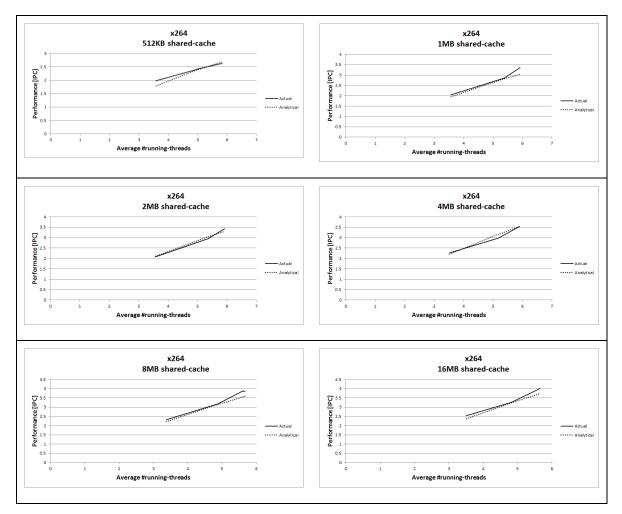

| 5.3.12. x264                     |     |

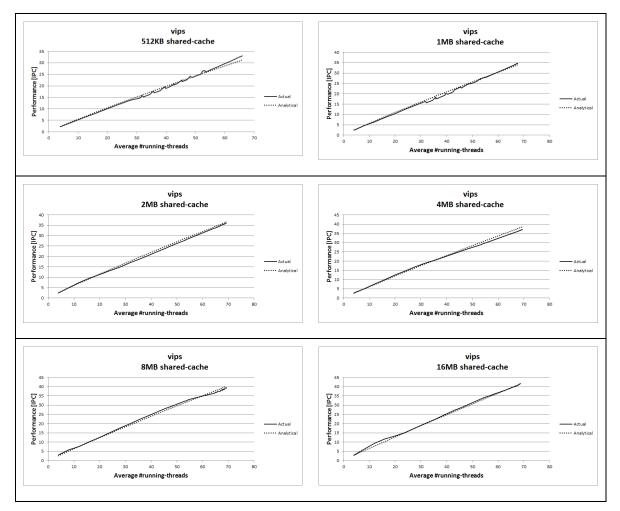

| 5.3.11. vips                     | 105 |

| 5.3.10. swaptions                | 103 |

| 5.3.9. streamcluster             | 100 |

| 5.3.8. raytrace                  |     |

| 5.3.7. fluidanimate              |     |

| 5.3.6. ferret                    |     |

| 5.3.5. facesim                   |     |

| 5.3.4. dedup                     |     |

| 5.3.3. Canneal                   | 86  |

# **List of Figures**

| Figure 2-1: Architecture model                                                    | 10    |

|-----------------------------------------------------------------------------------|-------|

| Figure 3-1: Application-Simulator interaction                                     | 19    |

| Figure 3-2: Weak memory consistency-model                                         | 24    |

| Figure 3-3: Functional execution scheduling                                       | 25    |

| Figure 3-4: The combination of functional and timing-model execution, resul       | lting |

| effectively an execution-driven simulation                                        | 26    |

| Figure 3-5 Execution scheduling with a dedicated thread for timing model execu    | ition |

| (T <sub>E</sub> )                                                                 | 27    |

| Figure 3-6 Execution scheduling without a dedicated thread for timing model execu | ition |

|                                                                                   | 28    |

| Figure 4-1: thread-context occupancy illustration                                 | 34    |

| Figure 4-2: Parallelism scalability - blackscholes                                | 38    |

| Figure 4-3: Running threads over time - blackscholes                              | 39    |

| Figure 4-4: Parallelism scalability – bodytrack                                   | 39    |

| Figure 4-5: Parallelism scalability – bodytrack (scaled)                          | 40    |

| Figure 4-6: Running threads over time - bodytrack                                 | 42    |

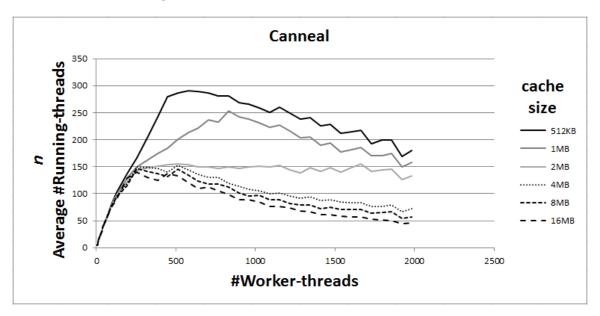

| Figure 4-7: Parallelism scalability - canneal                                     | 43    |

| Figure 4-8: Parallelism scalability – canneal (scaled)                            | 43    |

| Figure 4-9: Running threads over time - canneal                                   | 45    |

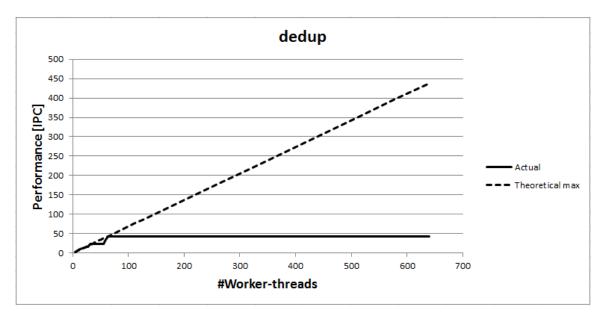

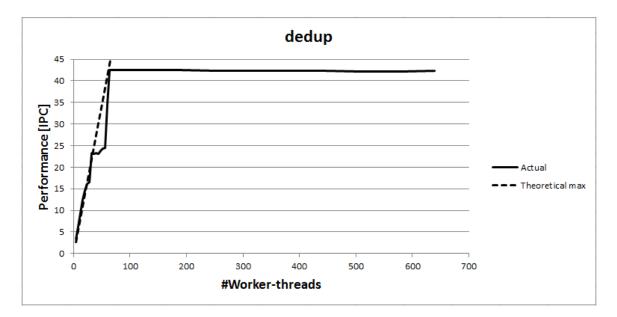

| Figure 4-10: Parallelism scalability – dedup                                      | 46    |

| Figure 4-11: Parallelism scalability - dedup (scaled)                             | 47    |

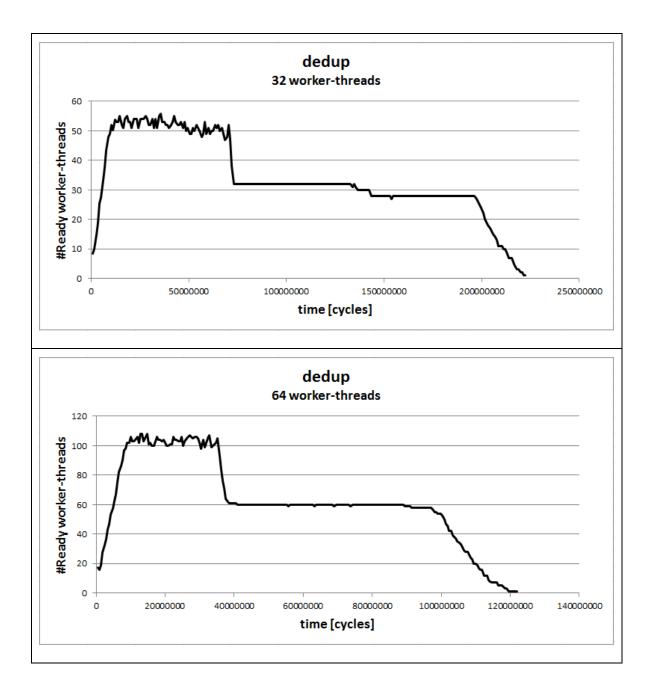

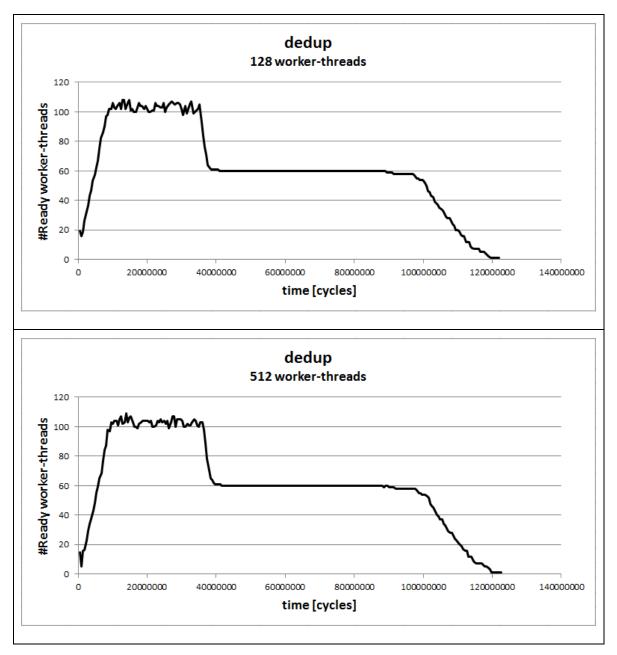

| Figure 4-12: Running threads over time - dedup                                    | 49    |

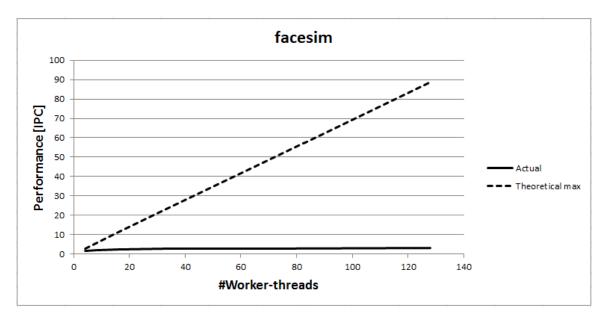

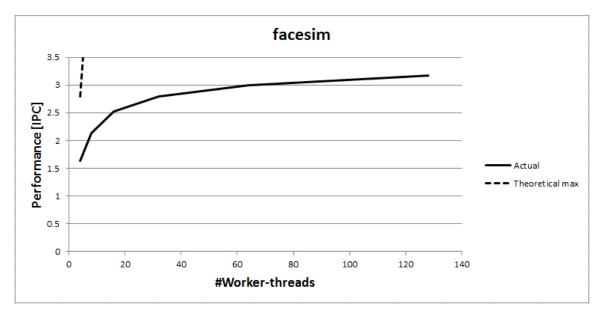

| Figure 4-13: Parallelism scalability – facesim                                    | 50    |

| Figure 4-14: Parallelism scalability - facesim (scaled)                           | 50 |

|-----------------------------------------------------------------------------------|----|

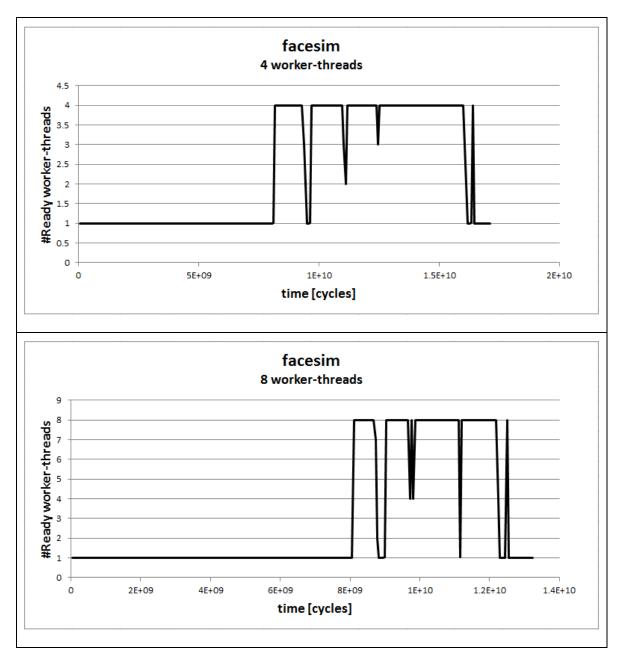

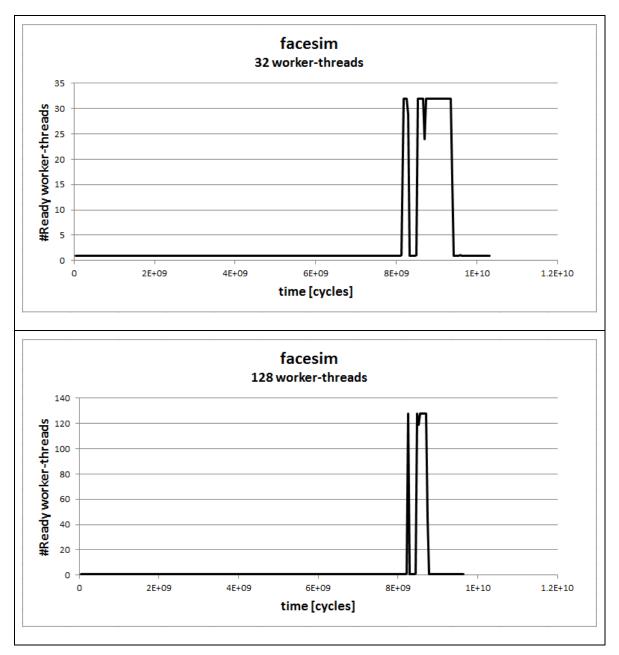

| Figure 4-15: Running threads over time - facesim                                  | 52 |

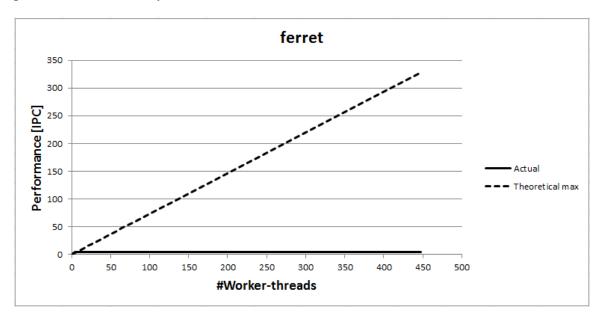

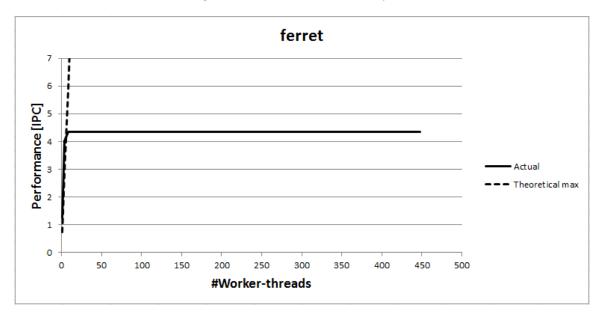

| Figure 4-16: Parallelism scalability - ferret                                     | 53 |

| Figure 4-17: Parallelism scalability – ferret (scaled)                            | 53 |

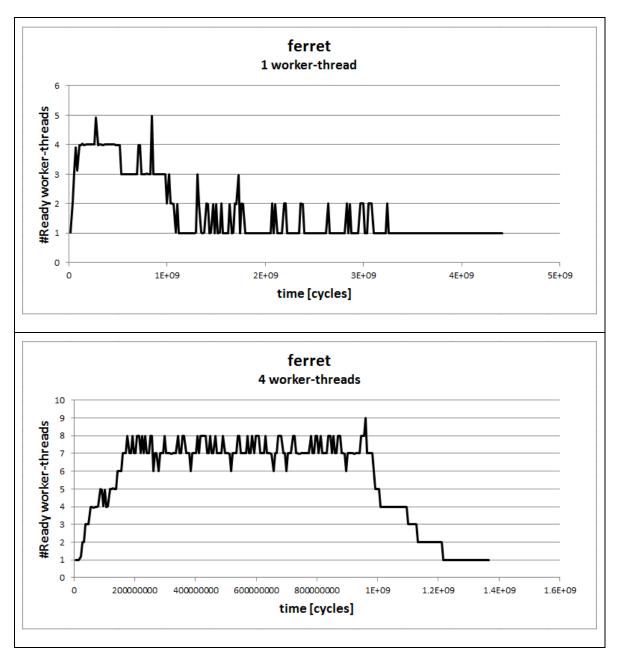

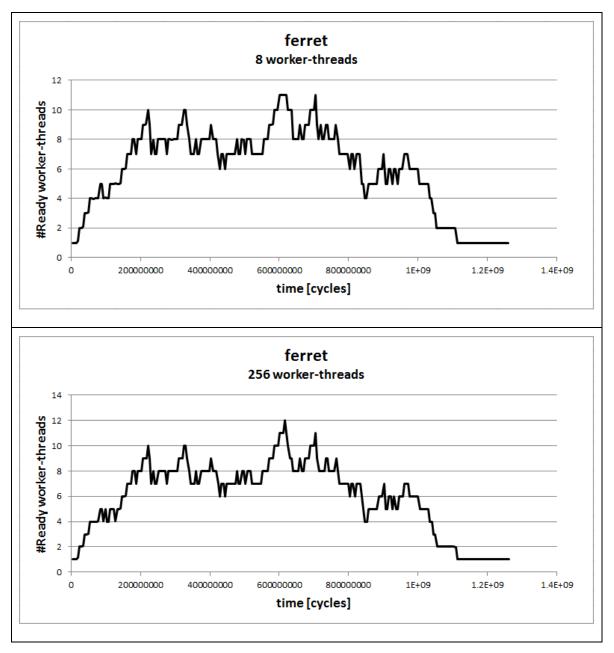

| Figure 4-18: Running threads over time - ferret                                   | 55 |

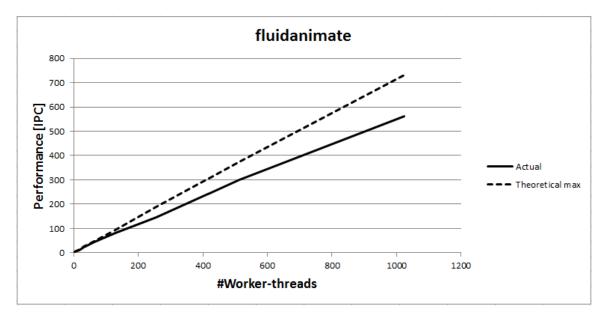

| Figure 4-19: Parallelism scalability - fluidanimate                               | 56 |

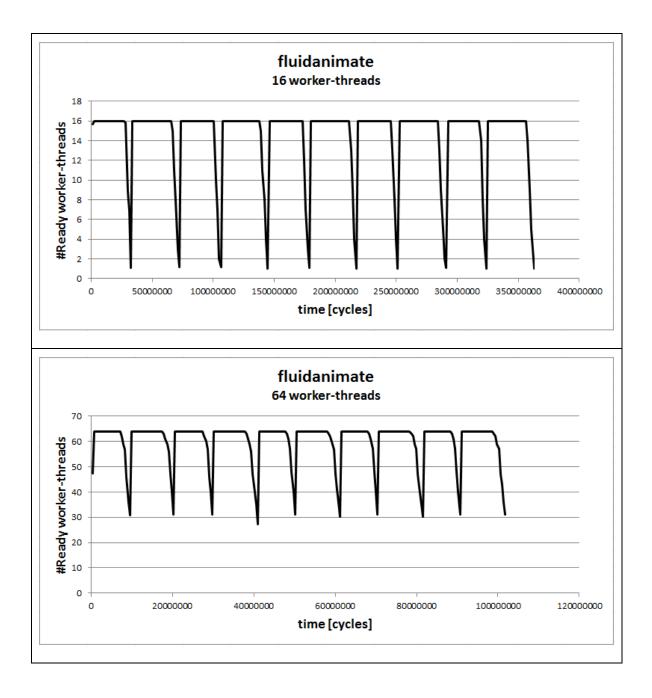

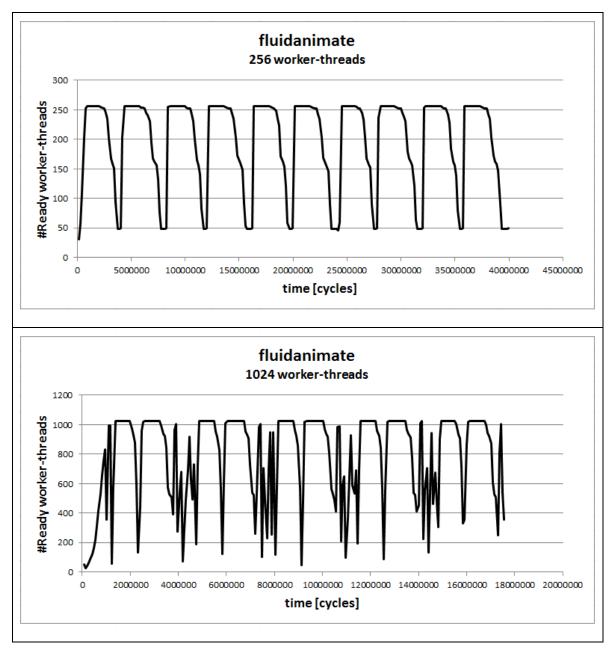

| Figure 4-20: Running threads over time - fluidanimate                             | 58 |

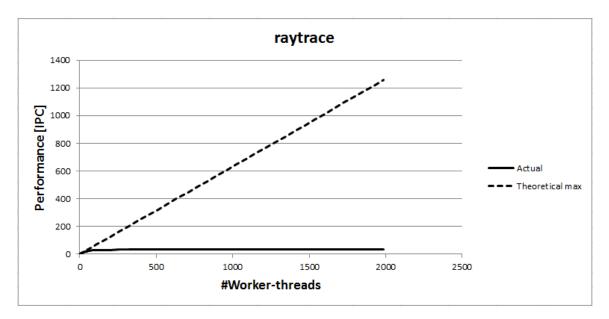

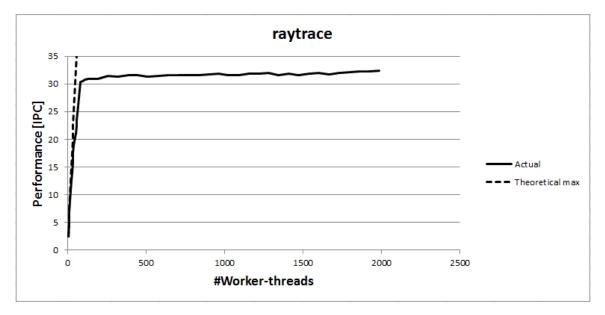

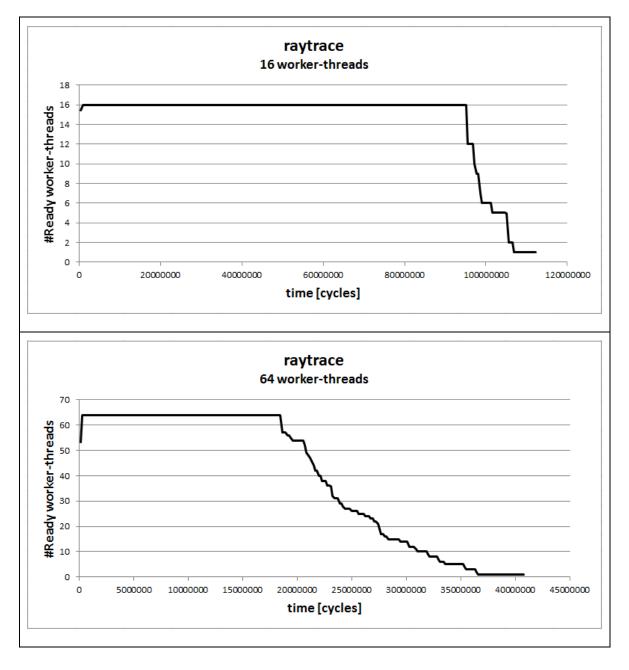

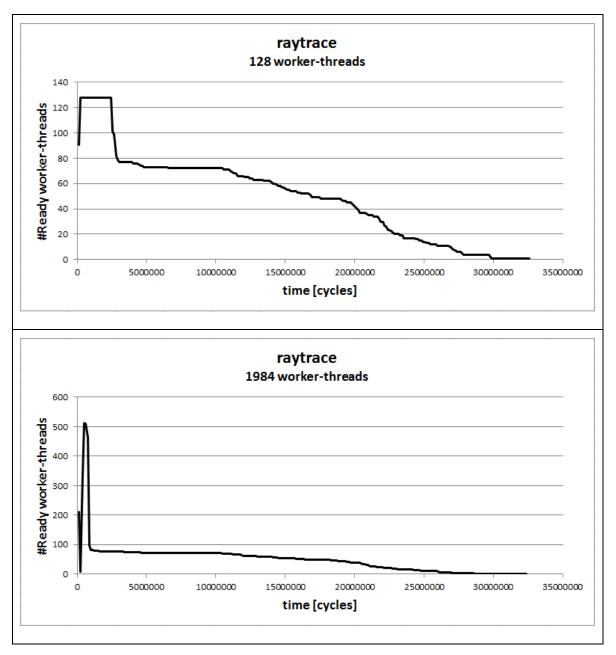

| Figure 4-21: Parallelism scalability - raytrace                                   | 59 |

| Figure 4-22: Parallelism scalability – raytrace (scaled)                          | 59 |

| Figure 4-23: Running threads over time - raytrace                                 | 61 |

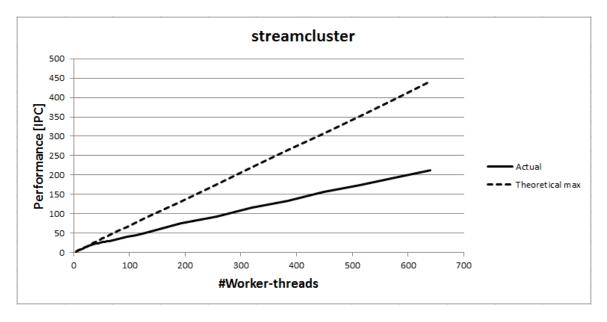

| Figure 4-24: Parallelism scalability – streamcluster                              | 62 |

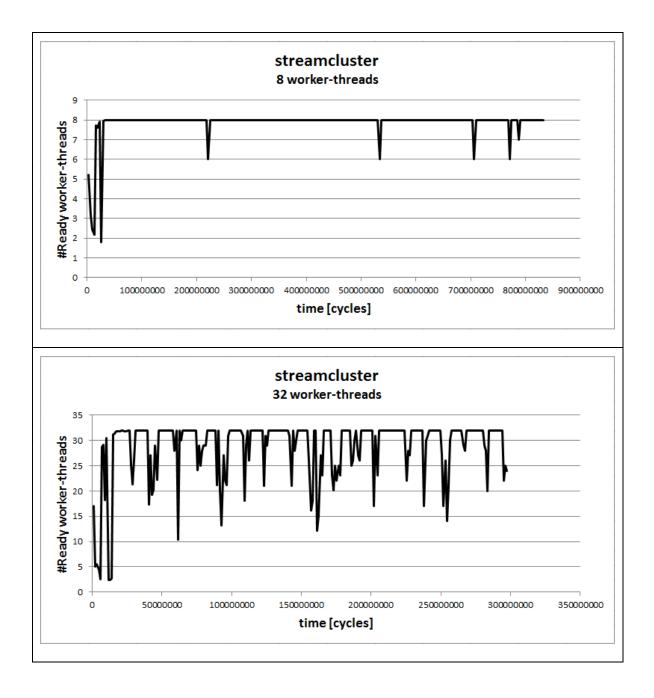

| Figure 4-25: Running threads over time - streamcluster                            | 64 |

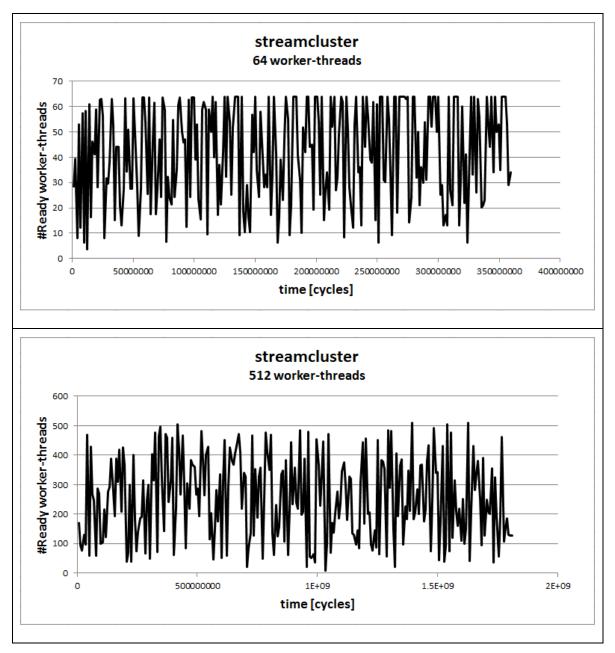

| Figure 4-26: Parallelism scalability - swaptions                                  | 65 |

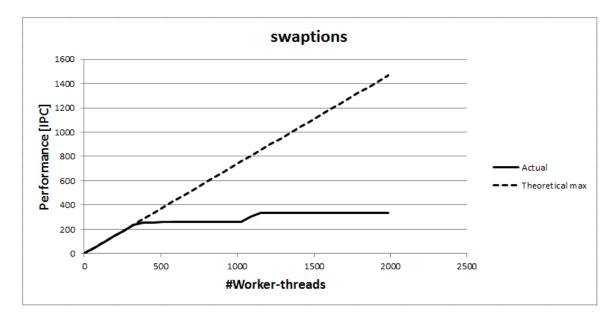

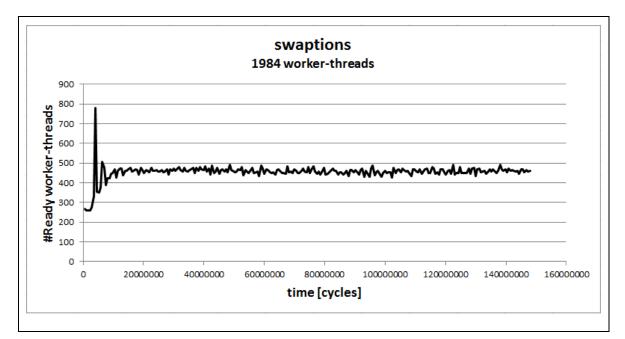

| Figure 4-27: Running threads over time - swaptions                                | 67 |

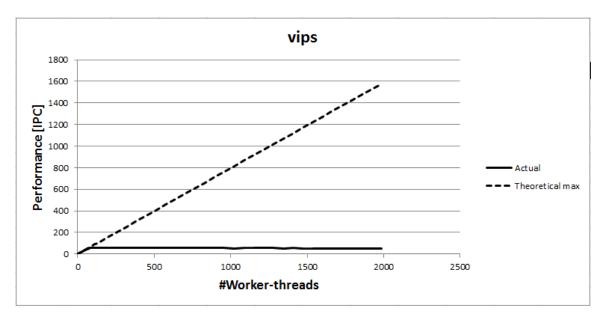

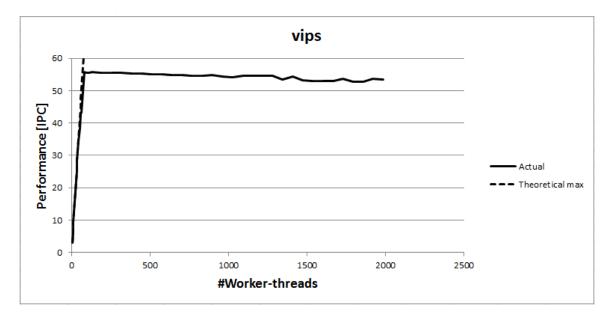

| Figure 4-28: Parallelism scalability - vips                                       | 67 |

| Figure 4-29: parallelism scalability – vips (scaled)                              | 68 |

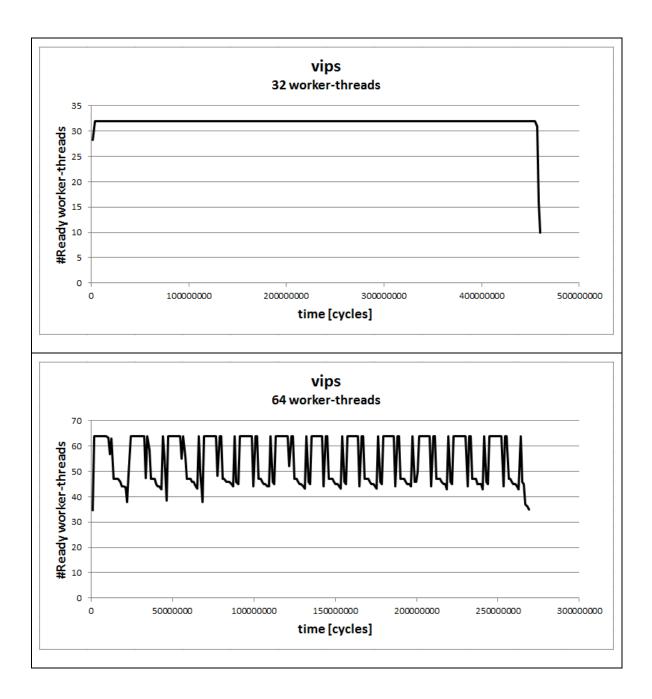

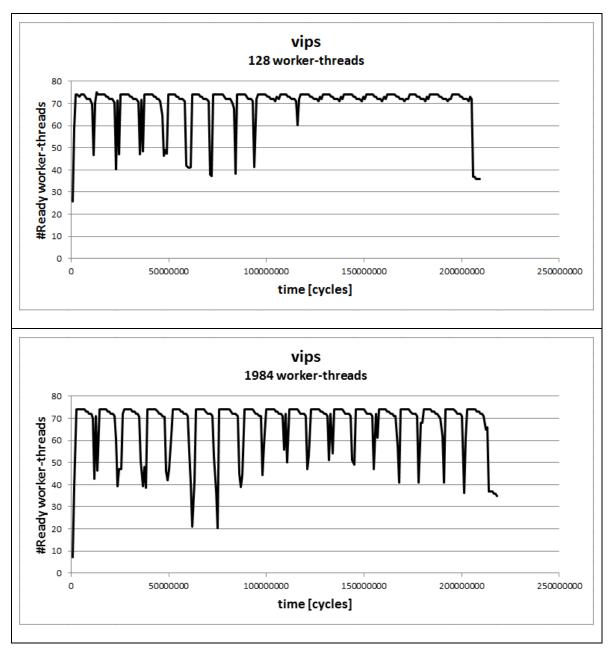

| Figure 4-30: Running threads over time - vips                                     | 70 |

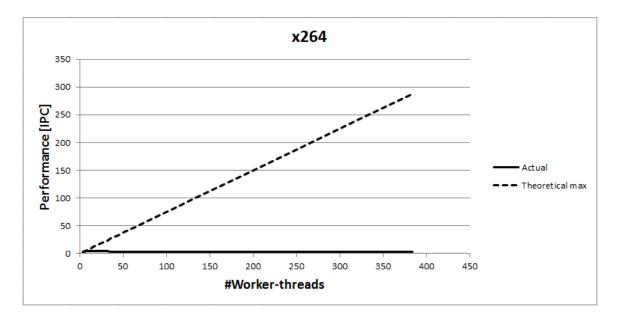

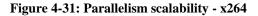

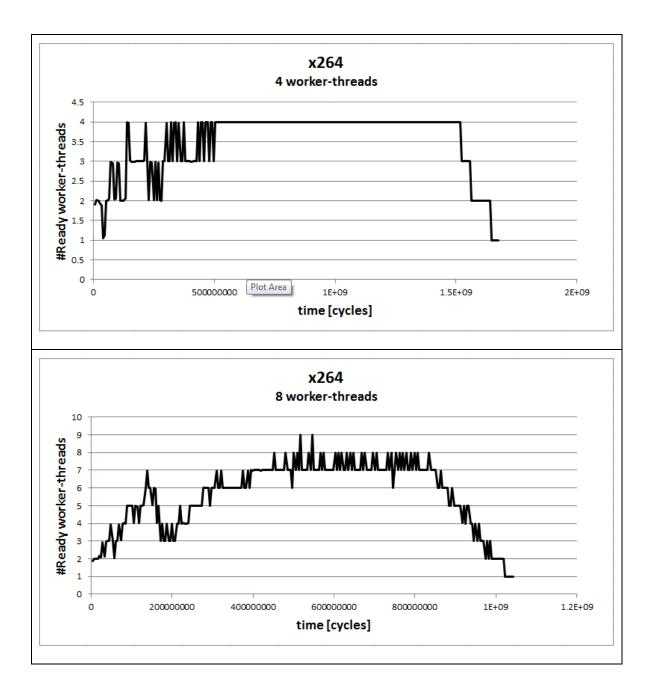

| Figure 4-31: Parallelism scalability - x264                                       | 71 |

| Figure 4-32: Parallelism scalability - x264 (scaled)                              | 71 |

| Figure 4-33: Running threads over time - x264                                     | 73 |

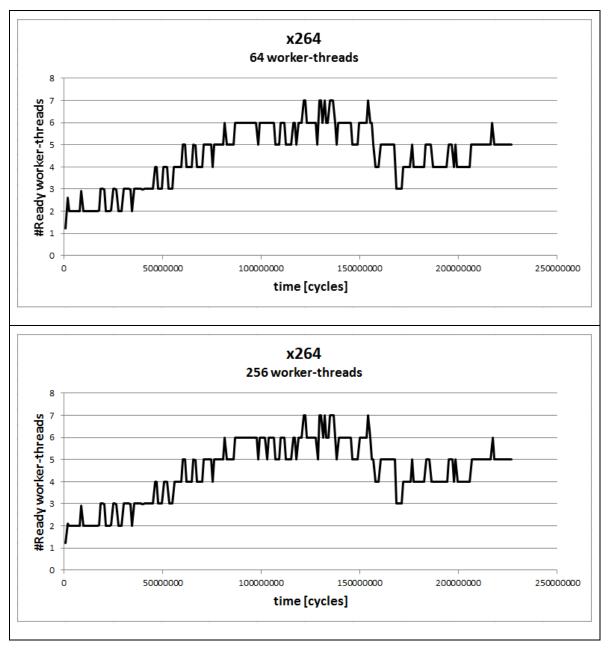

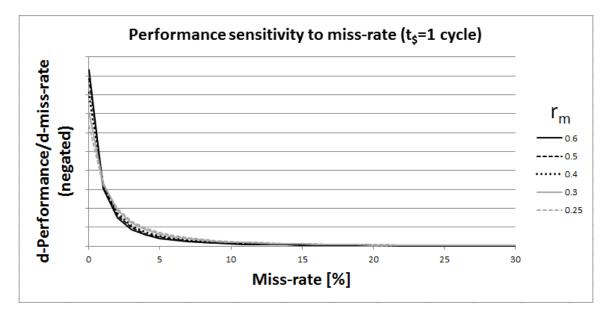

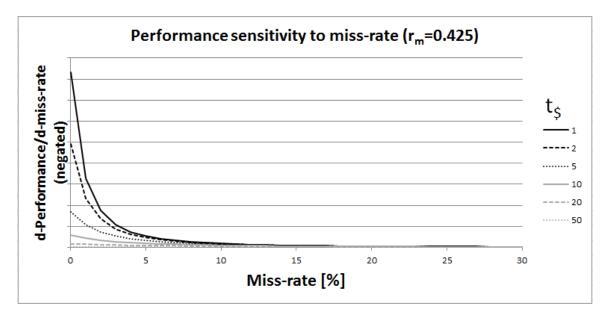

| Figure 5-1: Performance sensitivity to miss-rate for different values of $r_m$    | 80 |

| Figure 5-2: Performance sensitivity to miss-rate for different values of $t_{\$}$ | 81 |

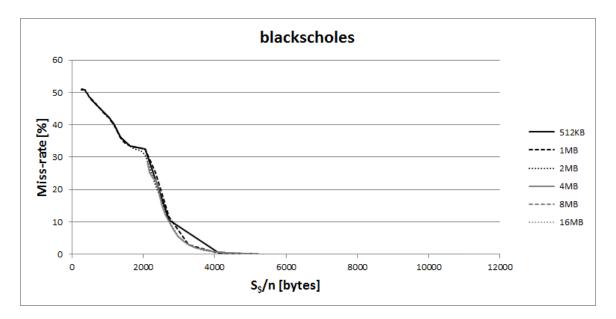

| Figure 5-3: Miss-rate from simulation – blackscholes                              | 82 |

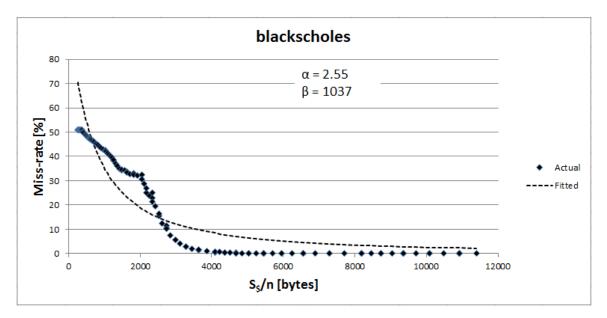

| Figure 5-4: Miss-rate model fitting – blackscholes                                | 82 |

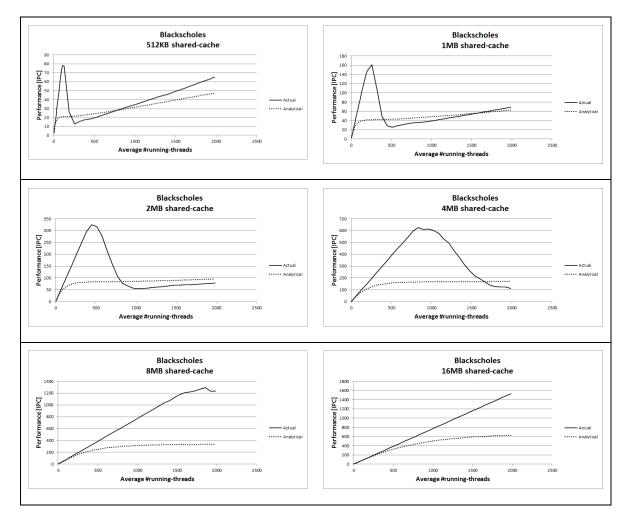

| Figure 5-5: Actual vs. analytical performance with different cache sizes - blackschole   |

|------------------------------------------------------------------------------------------|

| 82                                                                                       |

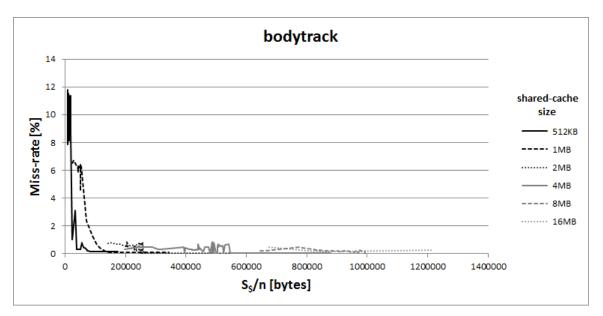

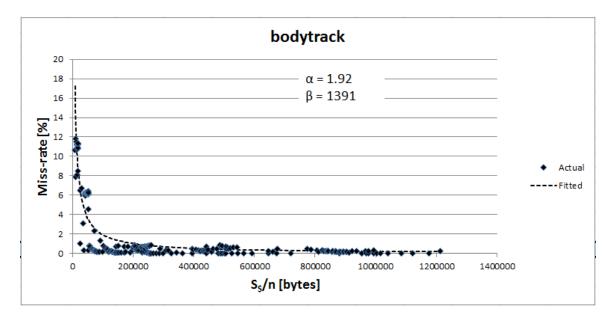

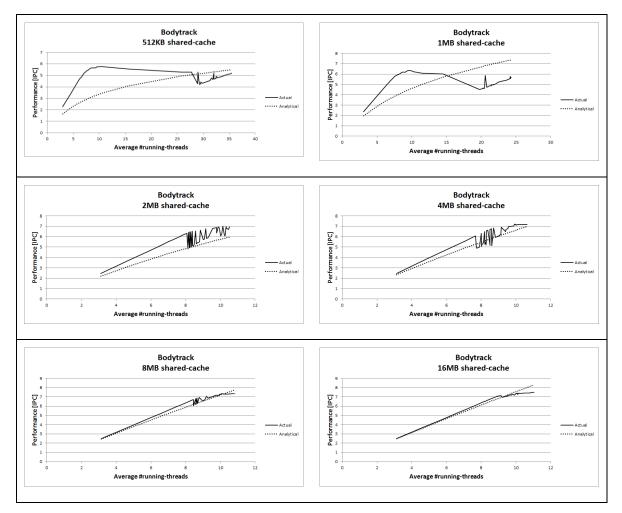

| Figure 5-7: Miss-rate model fitting – bodytrack                                          |

| Figure 5-8: Actual vs. analytical performance with different cache sizes - bodytrack 80  |

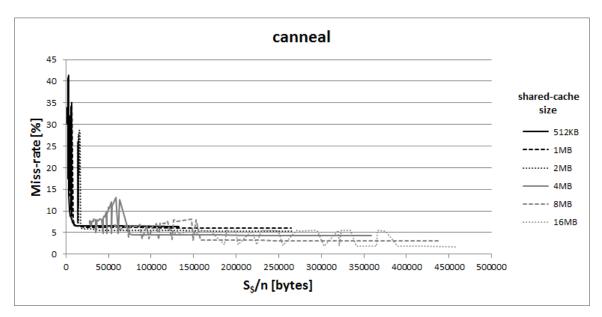

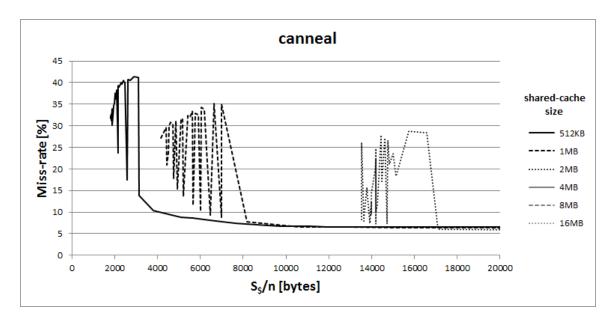

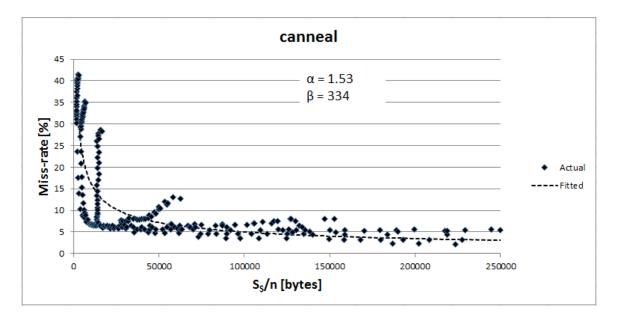

| Figure 5-9: Miss-rate from simulation – canneal                                          |

| Figure 5-10: Miss-rate from simulation – canneal (zoom)                                  |

| Figure 5-11: Average #running threads vs. #Worker-threads – canneal                      |

| Figure 5-12: Miss-rate model fitting – canneal                                           |

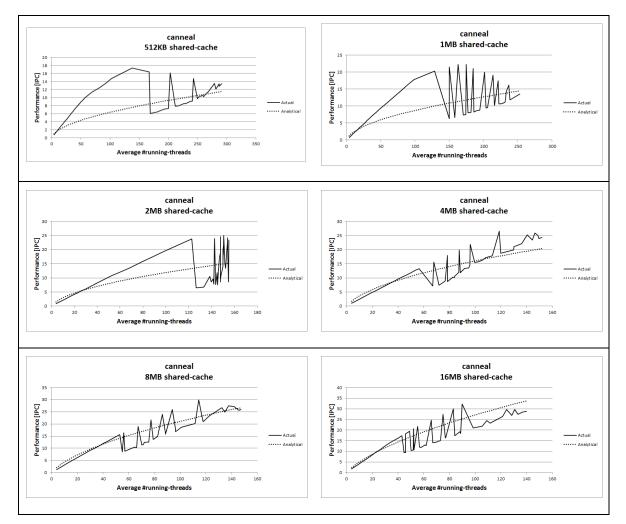

| Figure 5-13: Actual vs. analytical performance with different cache sizes - canneal 90   |

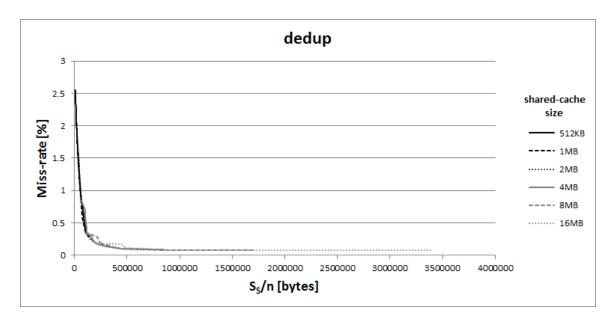

| Figure 5-14: Miss-rate from simulation – dedup                                           |

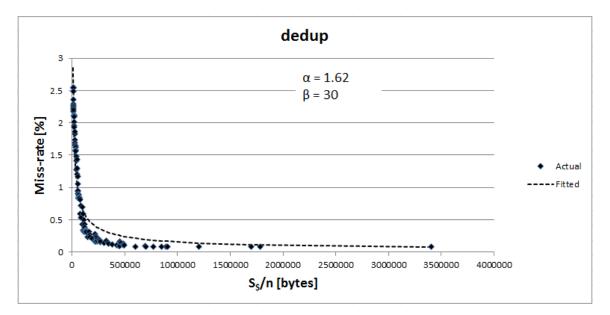

| Figure 5-15: Miss-rate model fitting – dedup                                             |

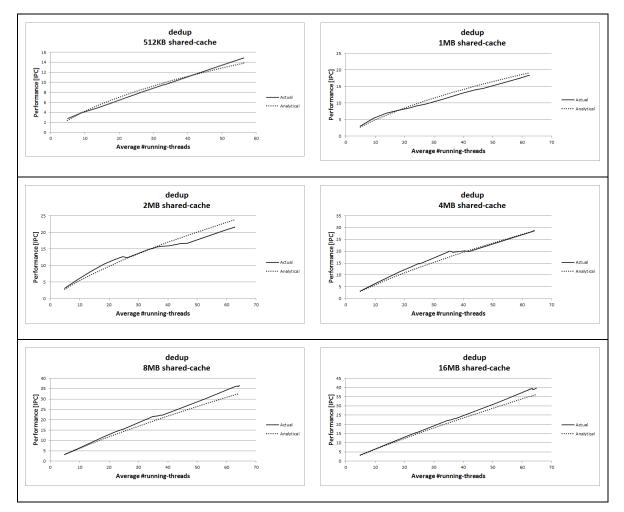

| Figure 5-16: Actual vs. analytical performance with different cache sizes - dedup 92     |

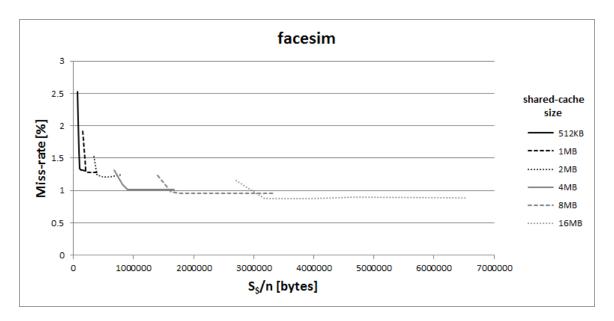

| Figure 5-17: Miss-rate from simulation – facesim                                         |

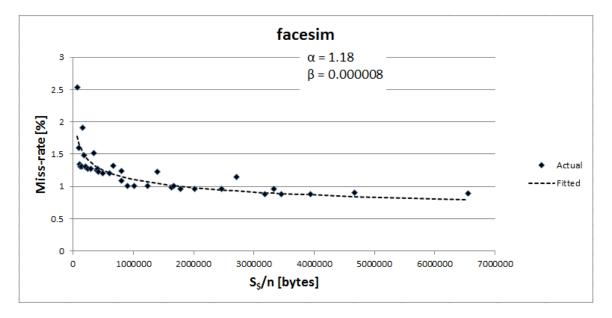

| Figure 5-18: Miss-rate model fitting – facesim                                           |

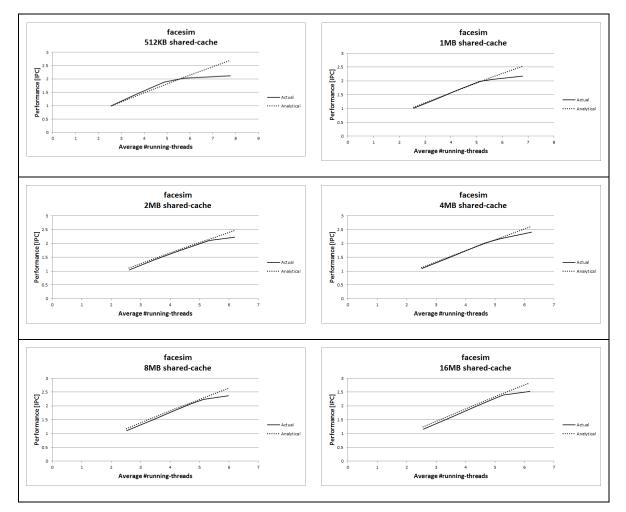

| Figure 5-19: Actual vs. analytical performance with different cache sizes - facesim . 94 |

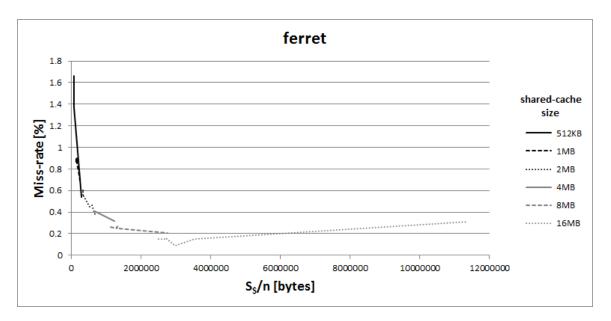

| Figure 5-20: Miss-rate from simulation – ferret                                          |

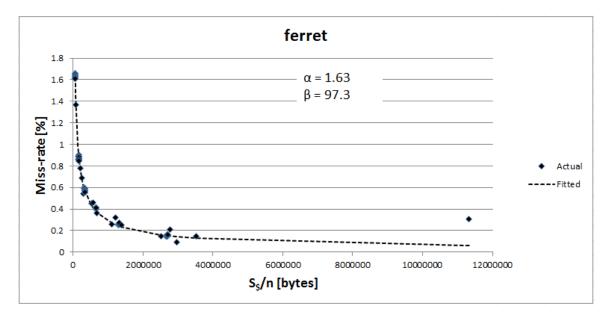

| Figure 5-21: Miss-rate model fitting – ferret                                            |

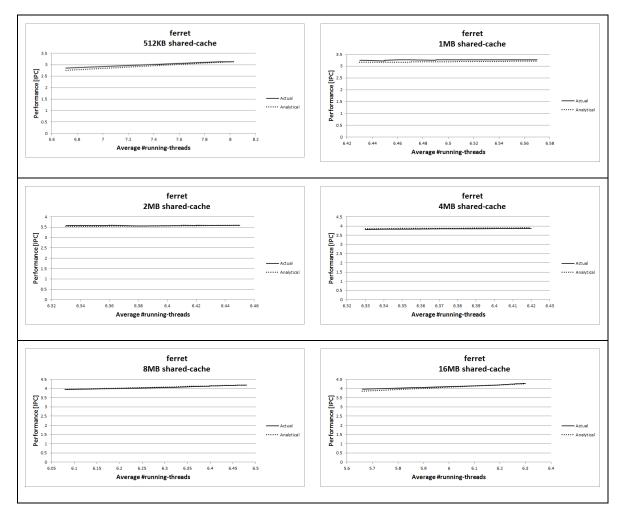

| Figure 5-22: Actual vs. analytical performance with different cache sizes - ferret 90    |

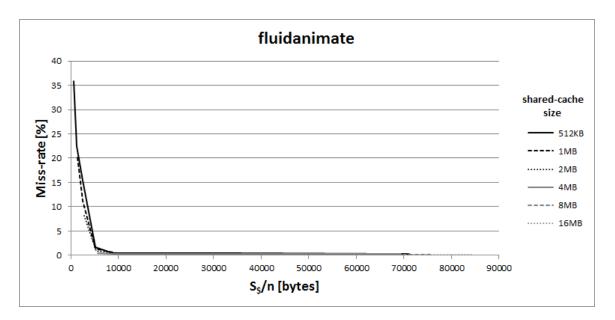

| Figure 5-23: Miss-rate from simulation – fluidanimate                                    |

| Figure 5-24: Miss-rate model fitting – fluidanimate                                      |

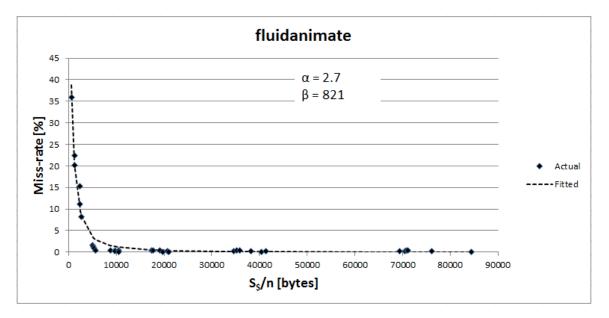

| Figure 5-25: Actual vs. analytical performance with different cache sizes - fluidanimate |

|                                                                                          |

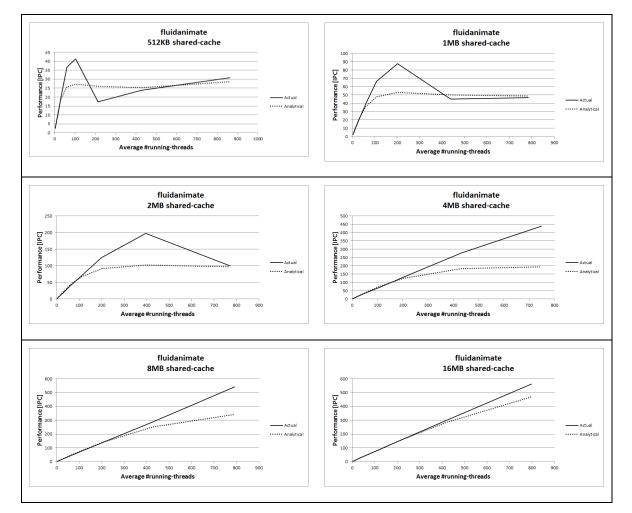

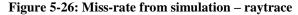

| Figure 5-26: Miss-rate from simulation – raytrace                                        |

| Figure 5-27: Miss-rate model fitting – raytrace                                          |

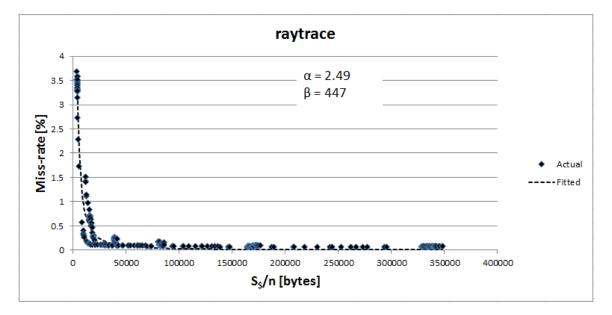

| Figure 5-28: Actual vs. analytical performance with different cache sizes - raytrace 100  |

|-------------------------------------------------------------------------------------------|

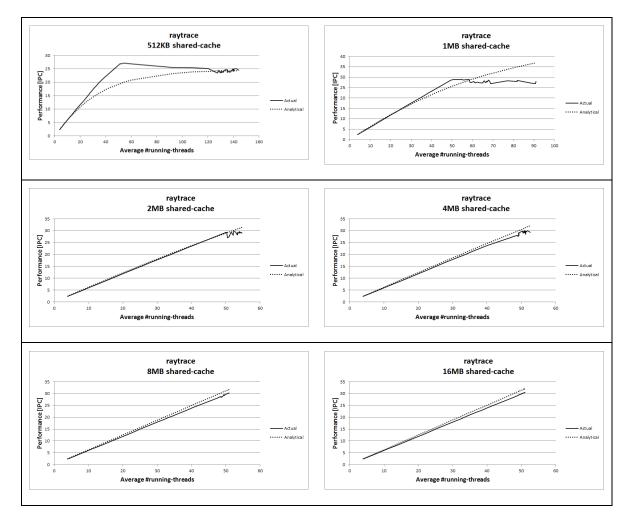

| Figure 5-29: Miss-rate from simulation – streamcluster 101                                |

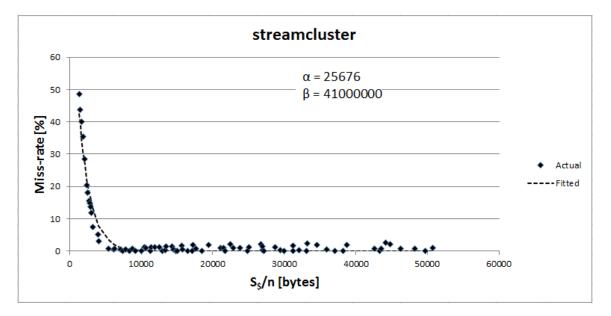

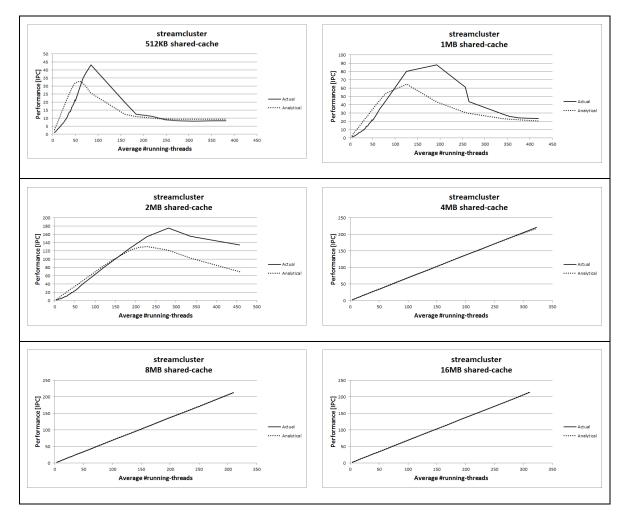

| Figure 5-30: Miss-rate model fitting – streamcluster                                      |

| Figure 5-31: Actual vs. analytical performance with different cache sizes - streamcluster |

|                                                                                           |

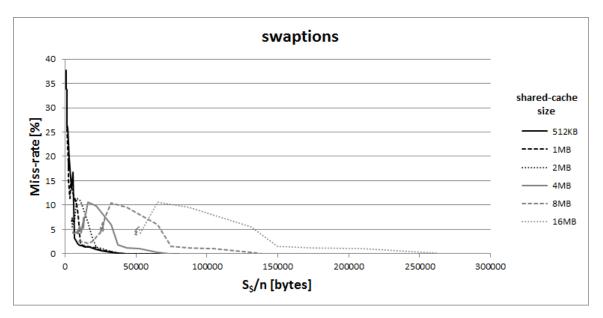

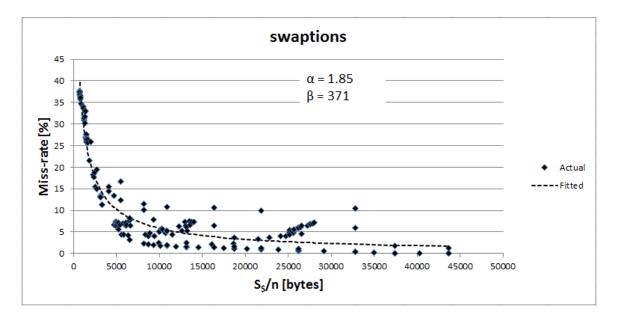

| Figure 5-32: Miss-rate from simulation – swaptions 103                                    |

| Figure 5-33: Miss-rate model fitting – swaptions 104                                      |

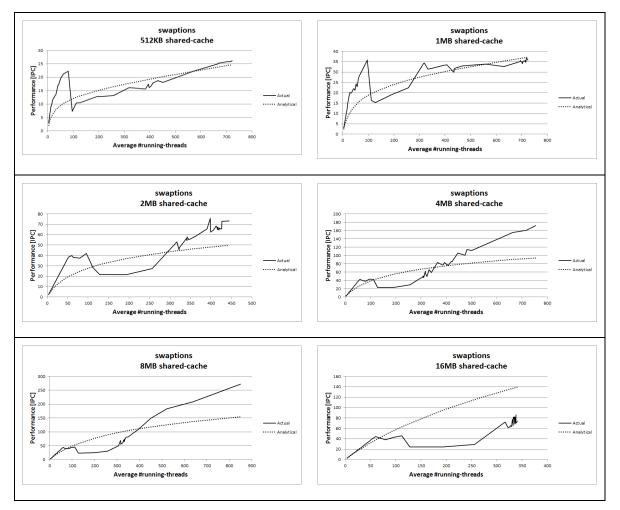

| Figure 5-34: Actual vs. analytical performance with different cache sizes - swaptions     |

|                                                                                           |

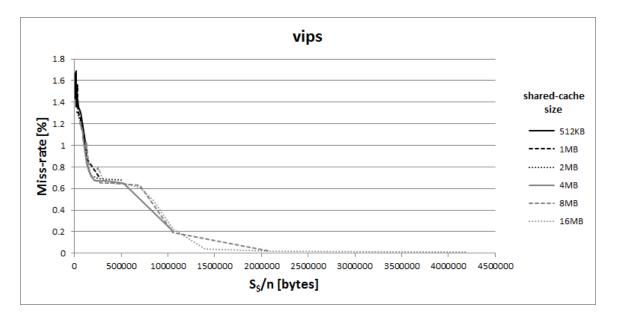

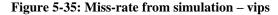

| Figure 5-35: Miss-rate from simulation – vips 106                                         |

| Figure 5-36: Miss-rate model fitting – vips 107                                           |

| Figure 5-37: Actual vs. analytical performance with different cache sizes - vips 108      |

| Figure 5-38: Miss-rate from simulation – x264 109                                         |

| Figure 5-39: Miss-rate model fitting – x264 110                                           |

| Figure 5-40: Actual vs. analytical performance with different cache sizes – x264 111      |

# **List of Tables**

| Table 2-1: System parameters                                      | . 11 |

|-------------------------------------------------------------------|------|

| Table 2-2: Workload parameters                                    | . 12 |

| Table 4-1: Model parameters for the parallelism scalability study | . 32 |

| Table 4-2: Parsec per-benchmark inherent parallelism limitations  | . 75 |

| Table 5-1 Model parameters for the cache modeling study           | . 79 |

### Abstract

Highly parallel architectures, such as GPUs or CPUs with vector instructions, require a lot of code tuning to achieve high utilization, i.e., in the order of the theoretical maximum performance. One of the main reasons is that due to technological limitations (e.g., power consumption, power density, availability of instruction level parallelism) highly parallel architectures trade off single-instructions-stream performance for maximum raw-performance. This puts a burden on the workload to provide enough parallelism to keep the architectural resources busy. While some workloads are inherently highly parallel (such as what is known as *embarrassingly parallel*), many interesting, compute-intensive workloads (animation, pattern recognition, ray-tracing) become harder to parallelize as the parallelism degree increases.

In this research we developed a simulator for highly parallel architectures (up to 2048 cores) that can simulate existing parallel benchmarks (any benchmark that runs on the Linux platform) and we use it to study a suite of interesting parallel workloads, the Parsec benchmark suite.

We characterize *parallelism scalability* of each benchmark, namely how the performance scales with the scaling of the architecture's parallelism (core count without overhead). We study another aspect of the Parsec benchmark suite -- shared cache performance (miss-rate) when running with high parallelism degree. We compare the actual performance to an analytical model proposed in the literature.

We find that the inherent parallelism scalability of the various benchmarks in the Parsec benchmark suite varies widely, from as poor as achieving peak performance at 4 threads (ferret) to unlimited, embarrassingly parallel (blackscholes). However the majority of benchmarks do not scale beyond 128 threads.

For cache performance, we find that while for most benchmarks it is compatible with a cache performance analytical model that is proposed in the literature, the performance is highly sensitive to the cache performance and therefore the small differences between the analytical and actual cache performance lead to large differences between analytical

performance estimation based on the analytical cache performance model and the actual performance.

# **Abbreviations**

- AMAT Average Memory Access Time

- EPTCS Effective Per-Thread Cache-Size

- LLC Last Level Cache

- LRU Least Recently Used

- IPC Instructions Per Cycle

- SMT Symmetrical Mutli-Threading

- ITC Inter-thread communication

## Chapter 1. Introduction

#### 1.1. Research overview

Contemporary CPU architecture trend for increasing performance is primarily towards increased parallelism, due to technological challenges such as power dissipation, power consumption, micro-architecture improvements etc. However, parallel architectures require the program to explicitly expose suitable degree of parallelism (e.g., number of threads) to be able to actually utilize the available architecture parallelism. Moreover, the parallelism needs to be exposed for the different type of resources such as utilize cores through threads, utilize cache through data working-set arrangement, utilize interconnect through communication/computation pipelining etc. Underutilization is the result of algorithmic dependencies such as data dependency, inter-task dependency, etc. Often, the situation is in between: part of the time the resources are fully utilized and the rest of the time they are underutilized. Adding resources may increase the performance during full utilization but the extent of the improvement is subject to Amdahl's Law [1], i.e., it depends on the fraction of full utilization periods and may be negligible.

Moreover, whether the architecture's resources are fully utilized and at what times during the program execution depends on the type of resource and on the structure of the program. For example, a program may have a certain data working set at certain times that may or may not fit in cache, depending on the amount of cache in the underlying architecture. If the working set doesn't fit in the cache, then a fast CPU will be underutilized because it can't access data fast enough to utilize its compute power. If the program reduced its working set it could achieve higher CPU utilization. Thus, matching the workload and the architecture can have a dramatic effect on the performance. This is more so with the high-performance architectures which have to tradeoff the amount of resources put into the architecture and technological limitations such as power consumption, DRAM latency, interconnect throughput etc. In this research we study some aspects of parallel benchmark on highly parallel architectures.

There are many aspects of benchmarks that can be measured and studied, at least one for each type of resource. We chose to study the first-order performance limiting factor of a parallel benchmark – its ability to utilize more cores. We study this for a diverse set of benchmarks of the Parsec benchmark suite [2][3]. We find the maximum number of cores that each benchmark can utilize on architecture with unlimited resources, thus we capture the inherent parallelism limitation of the benchmarks.

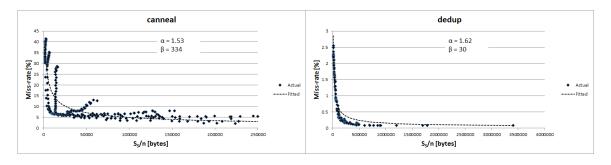

Another aspect of parallel benchmarks that we study is the effect of high parallelism degree on shared cache performance. With high parallelism degree and assuming independent parallel tasks<sup>1</sup>, the nature of the basic assumption that makes cache useful, namely locality-of-reference, changes. At the extreme, when no data is shared among the parallel tasks, the cache is effectively divided between the parallel tasks. This assumption can be used to construct an analytical model for shared cache performance (miss-rate) [4] We extract the actual cache performance from simulation and show that the analytical model for the cache performance is a good first-order approximation, nevertheless it is not ideal for analytical performance studies because the latter can be highly sensitive to the actual cache performance so that even a small mismatch between the analytical and actual cache performance results in a large mismatch between the analytical and actual performance.

#### **1.2. Summary of Contributions**

The main contributions of our research are:

- Construct efficient simulator for highly parallel architectures that can run any Linux benchmark.

- Identify and studying the maximal number of cores that each benchmark in the Parsec benchmark suite can utilize.

- Validating an analytical shared cache performance (miss-rate) model for highly parallel architectures.

<sup>&</sup>lt;sup>1</sup> Task independence is extremely important to minimize algorithmic dependency and therefore is a reasonable assumption for parallel workloads.

#### **1.3. Research Method**

Studying the interaction of highly parallel workloads and architectures requires simulating architectures with a parameterized degree of parallelism that scales to high numbers (hundreds and thousands of cores). Moreover, it requires benchmarks that are representative of parallel workloads. We use the benchmarks in the Parsec benchmark suite [3], which includes diverse workloads and provides control over the parallelism degree. For the architecture, we find that full-system simulators are not suitable for our purpose because these do not scale well to the parallelism degrees we want to study and the OS (Operating System) they run (general-purpose OS, typically Linux) does not support such high parallelism degrees. Furthermore, parallel benchmarks are computeintensive, hence OS kernel space processing is not only unessential to simulate, it actually constitutes noise because of compute resource consumption by background processing (e.g., interrupts, daemons). Therefore, we developed our own simulator that can execute Linux programs, and thus supports any Linux benchmark, and yet simulates only userspace code. We use this simulator to study the various aspects of workloads behavior, both global execution summary statistics and performance counters that reflect the behavior over time.

## Chapter 2. Many-core Architecture Model

#### 2.1. System Model

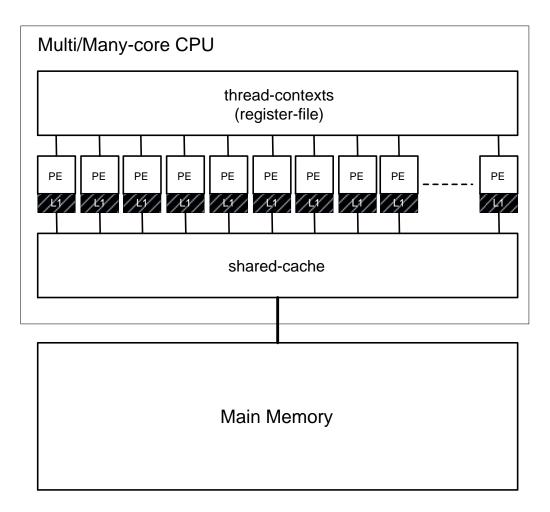

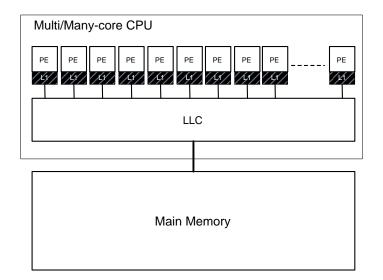

Our system model is the unified multi-/many-cores model defined in [4], depicted in **Figure 2-1**. It is a shared-memory system with an array of  $N_{PE}$  homogenous Processing Elements (PEs or cores) and a memory hierarchy that consists of PE-private caches (traditionally referred to as L1 caches) a shared cache (traditionally referred to as Last-Level-Cache or LLC) of size  $S_s$ , and main memory (RAM). It is a Symmetrical Multi-Threading (SMT) architecture system [5], i.e., has a register file with room for possibly more thread-contexts than PEs. A scheduler assigns thread-contexts to PEs and changes this assignment according to some scheduling policy (e.g., context-switch when a thread is stalled waiting for data from RAM). It should be noted that when the number of thread-contexts is equal to the number of PEs, the system is not an SMT one so non-SMT systems also map to this model.

Figure 2-1: Architecture model

The memory hierarchy model is a simple fixed-latency-per-hierarchy-level model with shared cache latency of  $t_s$  and main memory latency of  $t_m$ . The private cache latency is modeled indirectly in a workload parameter, discussed later.

The PEs are simple in-order cores with a fixed-latency for the computation part of the instructions denoted  $CPI_{exe}$ . A memory access adds the memory-hierarchy latency to the respective instruction latency. **Table 2-1** summarizes the parameters of the hardware architecture part of the model.

| Parameter        | Description                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------|

| N <sub>PE</sub>  | Number of PEs (in-order processing elements)                                                                         |

| S\$              | Cache size [Bytes]                                                                                                   |

| N <sub>max</sub> | Maximal number of thread-contexts in the register file                                                               |

| CPIexe           | Average number of cycles required to execute an instruction assuming a perfect (zero-latency) memory system [cycles] |

| tş               | Cache latency [cycles]                                                                                               |

| t <sub>m</sub>   | Memory latency [cycles]                                                                                              |

Table 2-1: System parameters

#### 2.2. Analytical Model

[4] defines an analytical model for the combination of the above system model and synthetic workload. A fundamental assumption of this synthetic model is that the task can be partitioned to any number of n sub-tasks, each handled by a separate thread. This assumption effectively ignores data-dependent variability.

The fraction of memory instructions in the synthetic workload's dynamic instructions stream is denoted by  $r^*_m$  ( $0 \le r^*_m \le 1$ ). Assuming the private cache miss-rate is  $P^*_{miss}$ , the fraction of instructions that access the shared cache is  $r_m = r^*_m \cdot P^*_{miss}$ . In particular, with no private cache (i.e.,  $P^*_{miss} = I$ )  $r_m = r^*_m$ .

The shared cache miss-rate depends on the specific workload characteristics (e.g., the working set, amount of data sharing between the threads), the number of threads n and the

size of the cache  $S_{\$}$ . The workload characteristics are captured in the miss-rate function  $P_{miss}(S_{\$}, n)$ . Table 2-2 summarizes the workload parameters.

| Parameter            | Description                                                                                           |

|----------------------|-------------------------------------------------------------------------------------------------------|

| n                    | Number of threads that execute or are in <i>running</i> state (not blocked) concurrently              |

| r <sub>m</sub>       | Fraction of instructions accessing memory out of the total number of instructions $[0 \le r_m \le 1]$ |

| $P_{miss}(S_{s}, n)$ | Miss-rate for cache of size $S_{\$}$ shared by <i>n</i> threads                                       |

#### **Table 2-2: Workload parameters**

In this model the only shared resource is the shared cache. Thus, the shared cache missrate function captures the shared resource contention effects of the interaction between the architecture and the workload. This analytical model does not capture the data dependency effects.

The parameters defined in **Table 2-1** and **Table 2-2** are used to analyze expected performance. In this context, for simplicity it is assumed that the workload parameters are fairly static, and do not vary much over time or space (i.e., between different threads of the same application). Therefore, the performance analysis uses average values in the equations below.

With no loss of generality, time is measured in cycles rather than in time units. This saves the need to incorporate the operational frequency into the analysis. Converting a result that is given in cycles units to the respective result in time units is straight-forward.

Given the per-thread shared cache miss-rate function and the cache and memory latencies as defined by the system model, the average number of cycles needed for data access, denoted  $t_{avg}$  (sometimes called Average Memory Access Time - *AMAT*) is given by:

(2-1)

$$t_{avg}(S_{\$}, n)[Cycles] = (1 - P_{miss}(S_{\$}, n)) \cdot t_{\$} + P_{miss}(S_{\$}, n) \cdot t_{m}$$

Formulating the average CPI is straight forward:

(2-2)

$$CPI_{exe}(S_{\$}, n) = CPI_{exe} + r_m \cdot t_{avg}(S_{\$}, n)$$

Assuming a thread scheduling policy of context-switch whenever a thread is stalled on a memory access, any given thread needs to stall once every  $1/r_m$  instructions on average, and wait until the data it accesses is received from memory. During this stall time, the PE is left unutilized, unless other threads are available to switch-in. The number of threads needed in order to fill a single PE's stall time, i.e., to saturate the PE, is:

$$(2-3) \quad N_{max} = 1 + t_{avg} \frac{r_m}{CPI_{exe}}$$

With all the PEs saturated, i.e.,  $n \ge N_{PE} \cdot N_{max}$ , each PE executes  $1/CPI_{exe}$  instructionsper-cycle (IPC) and the aggregate performance of all the PEs is thus  $N_{PE}/CPI_{exe}$ . With the PEs not saturated, i.e.,  $n < N_{PE} \cdot N_{max}$ , each thread executes  $1/CPI_{avg}(S_{s}, n)$  instructions-percycle so the aggregate performance of all the threads is given by:

(2-4) Performance

$$(S_{\$}, n)[IPC] = \frac{n}{CPI_{avg}(S_{\$}, n)}$$

Rewriting equation (2-4) in term of the model parameters we get:

(2-5) **Performance**(S<sub>\$</sub>, n)[IPC] =

$$\frac{n}{CPI_{exe} + r_{m} \cdot \{(1 - P_{miss}(S_{\$}, n)) \cdot t_{\$} + P_{miss}(S_{\$}, n) \cdot t_{m}\}}$$

#### 2.3. Simulation Model

We developed a simulator for the architecture model depicted in section 2.1. The simulated system includes an array of  $N_{PE}$  simple cores, with fixed latency per instruction<sup>2</sup>. Memory instructions suffer additional latency incurred by accessing the memory hierarchy, determined by a *memory hierarchy model*.

The memory hierarchy model consists of per-core private caches (L1), a cache that is shared by all the cores (Last-Level-Cache – LLC) and main memory (typically DRAM). Every level of the memory hierarchy is fixed latency and according to where the data is

<sup>&</sup>lt;sup>2</sup> Including branches – effectively assuming a perfect branch predictor.

found, the latency is added to the latency of the respective instruction. Thus memoryhierarchy contention effects are not modeled (e.g., bandwidth constraints; queuing effects).

There are  $N_{max}$  thread-contexts ( $N_{max} \ge N_{PE}$ ) and a scheduler that switches contexts when a thread stalls due to a memory operand that needs to be fetched from Main memory. Context switch takes zero time.

The analytical model depicted in section 2.2 is defined in terms of averages, thus it doesn't capture the effect of space and time variations. In particular it doesn't capture data-dependency effects. The simulation does capture the space and time variations effect because it actually executes the program and it does capture data-dependency effects through correctly simulating inter-thread synchronization: when a thread blocks through the OS (typically waiting on synchronization object), it is removed from the simulation scheduling, and once it is unblocked it is re-added. Thus simulation progresses with the blocked threads on one hand not making progress and on the other hand not consuming resources (compute, cache), which exactly matches the effects of the data-dependency.

Using this simulator we can study how real benchmarks behave under the architecture model depicted in section 2.1. Specifically, we can extract both architecture-level and workload-level statistics, with single cycle resolution. Examples for architecture-level statistics are core utilization, average memory access latency, context switch rate etc. Examples for workload-level statistics are instruction mix in the instruction stream (such as the  $r_m$  parameter for the analytical model, described in Table 2-2) memory access locality in space and time, inter-thread dependency such as synchronization etc. In particular, we use simulator statistics for extracting the workload-specific model parameters of Table 2-2, which themselves may depend on architecture parameters (which are therefore simulation parameters) such as cache size ( $S_s$  in Table 2-1).

## Chapter 3. The Simulator

In this chapter we present the simulator that we developed to study the behavior of existing benchmarks under the system model depicted in section 2.1. Our simulator executes native Linux benchmarks, and thus allows running standard benchmarks as well as custom benchmarks written in any of the abundant of programming tools that are available for Linux.

The simulator allows easy modifications of architecture parameters (e.g., core count, memory hierarchy configuration, cache configuration, etc.) and collecting comprehensive micro-architecture-level statistics (e.g., core stalls, cache lines utilization).

#### 3.1. Basic requirements

Our basic requirements for our simulator are that it runs Linux programs and that it simulates only the user-space execution. We argue that for the purpose of simulating benchmarks that target highly parallel architectures, simulating the kernel-space code execution is not only unnecessary, it's undesirable. In this section we explain the motivation behind these basic requirements.

Benchmarks that are not tied to a specific architecture are typically implemented for general-purpose operating systems, primarily Linux (but sometimes also for Windows and/or UNIX) to make them usable across many environments. In particular, there is an abundance of software development tools for general-purpose OSs, which facilitates implementing custom benchmarks as well as tweaking existing ones. Therefore, we target our simulator to be able to execute benchmarks implemented for Linux.

A straightforward approach for simulating a program implemented for a specific OS is a full system simulator [6][7][8], i.e., simulating an entire computer system and running a real-world operating system. However, in general, highly parallel architectures target compute intensive workloads. In fact, contemporary existing highly parallel architectures are typically used as accelerators [9][10], with no OS at all and no direct I/O capabilities<sup>3</sup>. Thus, simulating OS I/O services is not essential for throughput benchmarks.

Even when a throughput workload is running on a full-fledged OS, maximizing compute throughput typically involve preventing context switches to avoid the associated overhead. This is achieved by spawning no more threads than there are hardware thread-contexts. With this and under an assumption that no other programs are running on the system, no context-switch is needed, effectively neutralizing the OS scheduler. Thus, although the benchmarks we target for our simulator are implemented for a general-purpose OS (Linux), we assume that no OS-level scheduling is taking place so it's not necessary to simulate the OS scheduler.

Moreover, general-purpose OSs (such as Linux) perform background maintenance operations (interrupts, daemons) which trigger context-switches and consume core cycles, thus "polluting" the simulation with unrelated and non-deterministic computation resource consumption. As an example, in [11] a full-system simulator was used to gather traces for offline trace-driven simulation but the OS computation was filtered out of the trace because it was undesirable in the simulation.

Not all effects of OS services on throughput benchmarks simulation are undesirable. The effects of *Inter-Thread Communication* (ITC) such as locking, are essential for capturing the inter-thread data dependency, which can be a principal performance limiting factor in parallel workloads. Therefore, we target our simulator to be execution-driven (as opposed to trace-driven) to capture this important aspect of throughput benchmarks. However, we do argue that it's desirable to factor out the OS computation of ITC services in order to capture the workload's inherent data-dependency effects on the performance regardless of specific OS implementation of ITC services. ITC implementations are subject to various optimization tradeoffs that may be configurable or evolve between versions of the OS. Moreover, highly parallel architectures may implement ITC primitives in

<sup>&</sup>lt;sup>3</sup> In practice the benchmarks do use the OS I/O services, but primarily for setup (e.g., taking execution parameters) and teardown (e.g., reporting results) but the core of the benchmark doesn't use OS I/O services.

hardware. So we would like to preserve the effects of ITC on the simulated benchmarks without simulating their implementation.

To summarize, we want our simulator to simulate only the user-space code of the workloads, effectively assuming that all OS services (I/O or otherwise) do not consume computation resources but still preserve ITC effects.

An existing simulator that scales to the degree of parallelism that we need is Graphite [12]. However Graphite is optimized for low single-simulation latency and for that it exploits distributed setting. However, to facilitate distributed simulation, Graphite employs relaxed synchronization model. For our study, accurate synchronization is vital because synchronization can be a principal parallelism-limiting factor.

It should be noted that the simulation captures shared-resource contention effects, namely the memory hierarchy, similar to the analytical model, but it also captures the datadependency effects, by simulating the ITC effects, which the analytical model doesn't capture.

#### 3.2. Architecture

We implement user-space simulation by means of binary instrumentation. Binary instrumentation is the process of in-memory modification of a program while it executes, allowing interleaving of the program's code with custom instrumentation code that can observe and/or affect the original code's behavior. Binary-instrumentation-based simulation has the additional benefit of not requiring the simulated application to be implemented using a specific language or framework and doesn't require re-compilation. Among other things, this allows simulating applications that execute under a runtime-environment program such as the Java Virtual Machine. Our simulator is built on the Pin binary instrumentation framework from Intel [13].

#### 3.2.1. Functional execution scheduling

Since with binary instrumentation the application's instructions are functionally executed on a physical processor, the physical processor provides the ISA functional-

model. Thus, simulation requires the program instructions to be scheduled to the physical processor in the order imposed by the timing model of the simulated architecture. For example, when two threads contend on changing the same memory location (typically using atomic Read-Modify-Write instructions), the one that would execute first according to the timing model should be scheduled first to the physical processor.

Simulation is implemented through binary instrumentation by having the binary instrumentation framework instrument the benchmark program with simulator code that:

- observes the program's dynamic instructions streams (threads)

- executes a timing model of the simulated architecture on the observed instructions streams

- schedules the execution continuation according to the outcome of the timing model execution.

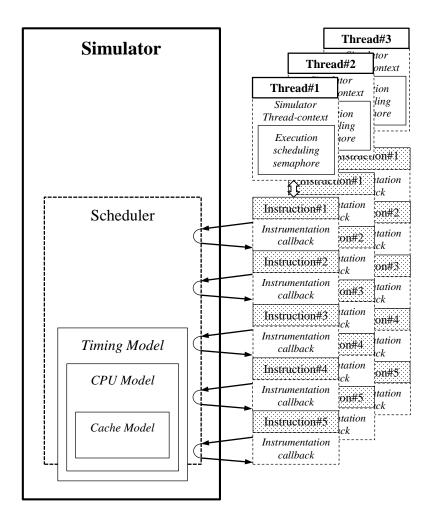

This is depicted in Figure 3-1. The instruction streams of the application threads are instrumented with callback operations into the simulator's code. These provide the simulator with all the information about the subsequent instruction of each instruction stream, such as whether it's a memory instruction or not, and if it is, whether it is a read or write operation, the referenced address, the operand size, etc. Therefore, as the code executes the simulator gets to see each instruction and its operands before it executes.

Figure 3-1: Application-Simulator interaction

To achieve the effect of execution-driven simulation, the instructions of the different threads must be executed in the relative order that the simulated architecture imposes. This means that the next instruction of a given thread must be allowed to execute only when it is determined that all the next instructions of all other running threads are ordered after it according to the simulated architecture's timing model. In other words, given a set of next instructions of all running threads, the next instruction to schedule for functional execution is the one that is going to complete first according to the timing model. Thus, given the set of next instructions of all running threads, the simulator executes the timing model until it determines which of these instructions will be completed first. Then it lets the respective thread execute this instruction. It then gets notified about the subsequent instruction of that thread, and it again has a set of next instructions of all running threads. It continues the execution of the timing model from where it left off and determines the next instruction that will be completed, and so on.

Controlling the next instruction execution requires the ability to suspend and resume application threads. This is achieved through a per-thread functional execution scheduling semaphore that is maintained in a per-thread-context block. When a callback is called with the information about the next instruction, the instruction is added to the current set of next instructions and the thread is suspended by waiting on its respective semaphore. When the next instruction to execute is determined from the timing model, the instruction is allowed to functionally execute by signaling the respective thread's semaphore, which make the callback return and the next instruction to execute.

#### 3.2.2. Inter-thread communication effects preservation

To further maintain execution-driven simulation, the ITC effects on the execution must be preserved. There are two main forms of ITCs: one that involves the OS and one that doesn't.

In ITC that involves the OS a thread makes a *syscall* (system call into the OS kernel) that blocks until another thread makes a complementary syscall that makes the former syscall return. When the blocking syscall is allowed to execute, the respective thread will get blocked inside the syscall. For the syscall to return, the other running threads need to be allowed to make progress in order for the complementary syscall to be reached. During this time the blocked thread cannot make progress. To reflect this, a thread that is about to execute a syscall is removed from the set of currently running threads. This allows simulation scheduling to continue because the timing model no longer expects to have a next instruction from that thread to participate in the timing model execution. When the complementary syscall is executed, the blocking syscall returns, which causes the instrumentation callback following the syscall to be called and the thread is added back to the set of running threads and it again participates in timing model execution and functional execution scheduling.

Instead of distinguishing between blocking and non-blocking syscalls to determine whether to exclude a thread from the set of running threads or not, we treat all syscalls as blocking. If the syscall is not really blocking, it will return quickly and the thread will be added back to the set. Under the assumption that non-ITC syscalls are rarely used in throughput workloads, the treatment of all syscalls as ITC should have negligible effect on simulation results.

The other form of ITC doesn't involve the OS, i.e., user-space-only ITC. Such ITC necessarily uses shared variables for the communication. The effects of such ITC are implicitly maintained by the user-space-only simulation as described above. The canonical example for user-space-only ITC is a spin-lock mutex [14]. A possible straight-forward implementation of spin-lock mutex is the following:

- 1 subroutine Acquire (Mutex)

- 2 while (CAS(Mutex.state, FREE, OWNED) = OWNED)

- 3 end while

- 4 End subroutine

- 5 subroutine Release (Mutex)

- 6 Mutex.state 🗲 FREE

- 7 MemoryFence

- 8 end subroutine

Since instructions are executed in the order imposed by the timing model, the thread that would execute the acquisition CAS first in the simulated architecture will be the one that is scheduled first by the simulator's functional execution scheduler and therefore end up owning the mutex first. Until the mutex is released all other threads will be spinning inside the Acquire subroutine and thus will not make computational progress, which is exactly the inter-thread data dependency effect that the simulator should capture.

#### 3.2.3. Achieving execution-driven simulation

The timing model part of our simulator is effectively a trace-driven simulator – its input is the instruction traces of the application threads. It so happens that the trace is of a single instruction from each thread. Once an instruction is executed, and therefore removed from the trace, the following instruction constitutes the next single instruction trace of that thread and again the input of the timing model is a trace of a single instruction from each thread. The online feedback from this trace-driven timing model to the trace collecting mechanism by mean of binary instrumentation callbacks makes our simulator effectively an executiondriven simulator.

The timing simulation is implemented using classical event-driven simulation design. From an architecture point of view, this allows arbitrarily detailed simulation, e.g., on-chip network routing, cache-coherency protocols, DRAM controller etc. This also allows trading off accuracy for simulation speed through a simplified timing model, e.g., fixed latencies memory hierarchy.

# 3.3. Implementation

#### 3.3.1. Reducing context switches

Following from the description in section 3.2.1, when two consecutively scheduled workload instructions are from different threads, there is at least one OS-level context switch because after the first instruction executes, the callback blocks on the semaphore and then the second instruction's thread semaphore is signaled and the respective thread unblocks. The more threads are running, the bigger the chance for any pair of consecutively executed instructions to come from different threads. So the number of context switches is in the order of the total number of executed instructions. This is a huge performance overhead.

A key observation here is that in order to preserve the effect of the simulated architecture's timing on the computation, it is not necessary to functionally execute all the instructions in the global order that is imposed by the timing model – it suffices that the functional execution order maintains the relative execution order. In particular, the

functional execution of a single thread is not affected by other threads if there are no shared operands. For example, suppose a thread  $T_A$  executes a computation sequence that involves only Register operands and no memory operand. The results of this sequence cannot be affected by computations of other threads because other threads cannot change any of  $T_A$ 's registers and therefore cannot change any of its operands. Thus, the results are not affected by whether other threads' computations are executed before, during or after  $T_A$ 's computation. In other words, this  $T_A$ 's computation sequence is unordered relative to other threads.

Similarly to register only operands sequences, if it can be shown that a computation sequence that uses memory operands do not share these memory operands with other threads, then such a sequence is also not affected by the execution of other threads and therefore is unordered relative to other threads. With Linux supporting processors with relaxed memory consistency models [15], i.e., modifications to memory locations may be observed in different order by different threads, the program must use memory fences to make any visibility order guarantees. While in theory different threads may observe fences from different other threads in different order (therefore also in non-real-time order), a simple fence ordering scheme that maintains the appropriate semantics is global real-time order, i.e., all fences are observed by all threads in the same order that also reflect their real-time order.

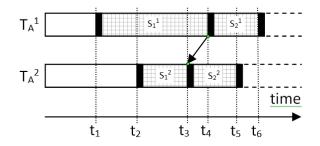

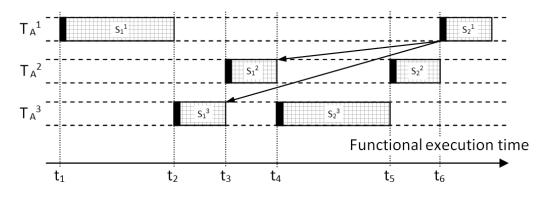

The order of memory modifications is defined relative to memory fences in their respective thread as depicted in Figure 3-2. It shows the real time execution of two threads  $T_A{}^1$  and  $T_A{}^2$ . The instruction streams are segmented on memory fence boundaries – the thick black lines denote memory fence instructions.  $S_1{}^1$  and  $S_2{}^1$  are consecutive segments of  $T_A{}^1$ . Similarly  $S_1{}^2$  and  $S_2{}^2$  are consecutive segments of  $T_A{}^2$ . The instructions in  $S_1{}^1$  are unordered relative to  $S_1{}^2$  – each may or may not see modifications made to shared variables by the other. The same is true for  $S_1{}^1$  and  $S_2{}^2$ . However, it is guaranteed that  $S_2{}^1$  sees the modifications made by  $S_1{}^2$  because  $S_2{}^1$  is ordered after the fence at t4, which is ordered after the fence in t3 (because fences are globally ordered), which in turn is ordered after  $S_1{}^2$ . So a segment  $S_m{}^i$  is guaranteed to see the changes made by a segment in another thread  $S_n{}^j$  IFF the memory fence preceding  $S_m{}^i$  in  $T_A{}^i$  is ordered after the memory fence succeeding  $S_n{}^j$  in  $T_A{}^j$ . Otherwise the segments are unordered. Therefore, correct programs

must ensure that there are no accesses with undefined relative ordering to the same operands by multiple threads because otherwise, the same initial program state may produce different results in different runs.

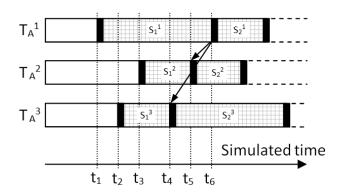

Figure 3-2: Weak memory consistency-model

Whether unordered segments see the memory modifications of each other is undefined. Therefore, they cannot have common operands. Thus, unordered segments can be functionally executed in any order with no change of semantics, i.e., independent of their exact timing according to the timing model. To maintain correct execution semantics it suffices that ordered segments are functionally executed in the right order according to the simulated architecture timing model and for that it suffices that only memory fences are executed exactly according to the timing model. This allows functionally executing instructions of a single thread atomically (i.e., continuously) without considering the timing model as long as no memory fence is encountered. Once a memory fence is encountered, its functional execution must be delayed until all memory fences that precede it according to the timing model have been executed so that subsequent instructions get to see the functional results of other threads' segments that are ordered before them. This is illustrated in **Figure 3-3**. It shows 3 instructions streams of 3 threads:  $T_A^1$ ,  $T_A^2$  and  $T_A^3$ . The small black rectangles denote instructions that are memory fences. Figure 3-3(a) shows the functional execution timing in the simulated architecture. The arrows show order dependency, from a segment that is ordered after to the segments that are ordered before it. Figure 3-3(b) shows functionally equivalent execution: memory fences are executed in the same order as in **Figure 3-3(a)** and segments that are ordered execute in the right order.

(a) Simulated architecture execution timing

(b) Valid observed functional execution of (a) under week memory consistency model

#### Figure 3-3: Functional execution scheduling

Segment execution includes trace collection. The timing model still works with one instruction trace per thread but after an instruction is determined to be completed, the next instruction for that thread is taken from the respective thread's trace, if it's not empty. If it is empty, the next segment is allowed to execute and a new trace is collected. Now again there are non-empty traces for all the running threads and the timing model execution can continue.

#### 3.3.2. Timing model execution thread

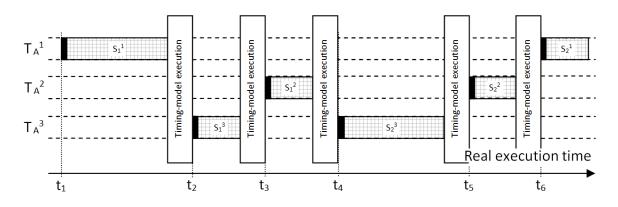

**Figure 3-4** depicts how the functional-execution scheduling is combined with timing model execution to achieve the effect of execution-driven simulation. When an application code segment executes, a trace is collected. Timing simulation takes place when a non-

empty trace is available for all running threads. During timing simulation all the threads are blocked on their execution scheduling semaphore. The exhaustion of any of the perthread traces implies that the next instruction in that thread is next in the global order. At this point timing simulation is suspended and functional execution of the thread whose trace was exhausted is resumed and a new trace is collected, up to the next fence (excluding). Now again there are non-empty traces available for all running threads and again timing simulation can take place.

Figure 3-4: The combination of functional and timing-model execution, resulting effectively an execution-driven simulation

To summarize, the simulator alternates between two execution phases:

- I. Functional execution and Trace-collection

- II. Timing-simulation

In phase I, the workload's code executes on the physical processor (functional execution) and the instrumentation code collects trace by observing the instructions stream. Once traces are collected for all running threads, simulation changes to phase II by suspending the functional execution (all threads are blocked on their respective execution scheduling Semaphore) and executing the timing simulation. Once the timing simulation exhausts any of the thread traces, simulation changes back to Phase I by suspending the timing simulation and resuming the execution of the thread whose trace was exhausted by signaling its execution scheduling semaphore. After the resumed thread collects a new trace, once again traces are available for all threads and timing simulation can continue and so on.

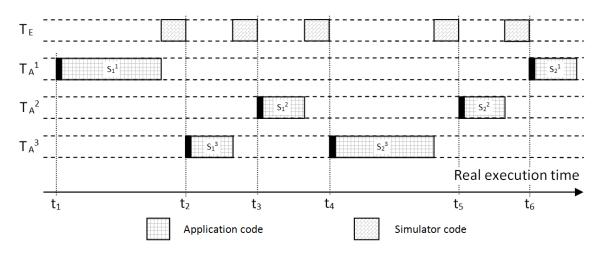

Executing the timing model requires an execution thread-context. One possible approach is to have a dedicated thread  $T_E$ . That thread would determine the next instruction to execute, unblock the respective thread  $T_A{}^i$  and wait for it to complete collecting a new trace for that thread. When trace collection completes, the callback of that thread will make the trace available to  $T_E$ , unblock it and then block on its scheduling semaphore. This is depicted in Figure 3-5.

Figure 3-5 Execution scheduling with a dedicated thread for timing model execution (T<sub>E</sub>)

This approach implies that for every executed segment there will be two context switches: one from  $T_E$  to  $T_A{}^i$  after  $T_A{}^i$  has been determined from the timing model and one from  $T_A{}^i$  to  $T_E$  once trace collection for  $T_A{}^i$  completes.

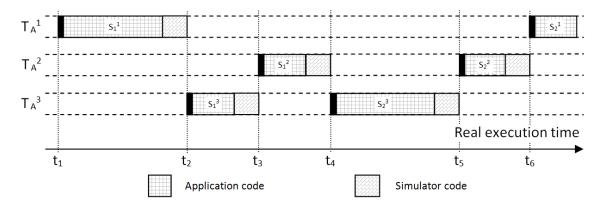

It should be noted that in this approach the execution of  $T_E$  is completely serialized with the execution of the application's threads – when one executes all the others are blocked. Therefore, we exploit this fact to save one context-switch per-segment by executing the timing model in the application thread within the callback. This is depicted in Figure 3-6.

Figure 3-6 Execution scheduling without a dedicated thread for timing model execution

#### 3.3.3. Limiting the size of a segment

We saw that partitioning instruction streams into segments along memory fences and executing the segments atomically is consistent with weak memory consistency model and also allows incurring only one context switch per segment execution. However, a thread may execute an unbounded number of instructions between memory fences, implying that segments lengths are unbounded which in turn implies that trace lengths are unbounded. Long traces increase the memory working-set, potentially incurring significant overhead (e.g., reduces cache utilization, thrashes physical memory). Also, the marginal gain of amortizing the context-switch overhead across long segments diminishes quickly – for example the gain in amortizing the context switch overhead across segments of 20 instructions instead of 10 instructions is much larger than the gain in amortizing across 1010 instructions instead of 1000 instructions. Therefore, it is beneficial to limit the segment length (and therefore the trace length) – it avoids the overhead of larger memory working set on the expense of negligible context-switch overhead due to what could have been a longer segment.

It is important to note that in general, the segment-based functional execution scheduling ensures that first instructions in each segment are executed in the global order that is dictated by the timing model (which is not the case with instructions that are not first in a segment). Thus, instructions that must execute in the correct global order, such as memory fences, must be first in an execution segment. However, any instruction can be executed in the correct global without affecting correctness. So a segment can be made arbitrarily short without affecting correctness, as long as memory fences are always first in a segment. In particular, a segment can be limited to 1 instruction, thus making all instructions first in a segment and hence all instructions are executed in the correct global order, as would be the case if we didn't employ longer traces. This also allows suspending trace collection conservatively, i.e., if an operation may be a fence but not necessarily, e.g., a syscall.

The actual trace length limit is a parameter of the simulator.

#### 3.3.4. Simulated architecture software scheduling

As explained in section 3.1, it is assumed that a throughput workload will not spawn more threads than there are hardware thread-contexts in the simulated architecture and therefore there is no need for a software scheduler, i.e., software-managed contextswitching, a software scheduler that suspends a running thread to free its hardware threadcontext and assigns another thread to that thread-context. However, in practice a workload may have more active threads than hardware thread-context even if it doesn't spawn more worker thread than there are thread-contexts. For example, a workload may have a main thread than spawn the worker threads and then waits for them to terminate. If all the worker threads start running before the main thread reaches the blocking step, there are more active threads in the program than there are hardware thread-contexts. The simulator handles this by implementing a simple cooperative-multitasking software scheduler i.e., a scheduler that holds aside threads if there is no vacant hardware thread-context and map them to a hardware thread-context when one becomes available, i.e., by a running thread getting blocked on an OS syscall. Thus, in the above workload example where the number of running threads is one more than there are hardware thread-contexts, either the main thread is assigned to a hardware thread-context or it is not. If it is, then one of the worker threads cannot be mapped to a hardware thread-context and therefore the main thread can make progress but one of the worker threads cannot. The main thread will quickly get to block waiting for the worker threads to finish and hence will free its thread-context and the cooperative scheduler will assign the last worker thread to that thread-context. Now only the worker threads are active and therefore all are assigned to thread-contexts, all run in parallel and no further context switch is needed even if any of them blocks. If the main thread is not assigned to a thread-context (for example, because it blocked on something else and then unblocked before blocking on waiting for the worker threads to finish) then all the worker threads are assigned to hardware thread-contexts and they all run in parallel until one of them blocks or terminates. When one blocks or terminates, its thread-context is freed and the cooperative scheduler assigns the main thread to it. Again the main thread will quickly get to the stage that it is blocked on the worker threads and again only worker threads are active so there are at most as many active threads as there are thread-contexts and the worker threads run in parallel until termination. Thus, in either case the worker threads end up running in parallel except for brief period it takes for the main thread to block after spawning all the worker threads.

It should be noted that this software cooperative scheduler graceful handling of the number of active threads exceeding the number of hardware thread-contexts is not limited to exceeding only by one. It can be easily seen that exceeding by more than one is handled equally gracefully, as long as the period of excessive active threads is very small relative to the runtime of the worker threads.

# 3.4. Summary

To summarize, our simulator executes Linux programs, simulating only the user-space code. It is oriented to throughput workloads, assuming no use of OS I/O or scheduling services. The functional execution is provided by the physical processor and the timing simulation is provided by an arbitrarily detailed timing model that is implemented using event-driven architecture.

# Chapter 4. Benchmarks parallelism scalability study

## 4.1. Introduction

In this chapter we use our simulator to study the inherent parallelism scalability of a widely used parallel benchmarks: the Parsec benchmark suite [3]. What we would like to capture is the benchmarks' inherent limitations in exploiting highly parallel architectures. We capture this through the performance as a function of the degree of parallelism that is available in the underlying architecture (the number of Processing elements or Cores).

To capture the parallelism inherent in a benchmark's algorithm, we use architecture with no inherent parallelism limitation in the architecture itself, such as bandwidth limits or memory latency. Therefore, for the parallelism scalability study we use architecture with a perfect memory system – no cache and every memory access incurs a latency of 1 cycle. We maintain a latency of 1 rather than 0 cycles as an expression of the fact that memory instructions are inherently slower than non-memory instructions.

The metric we use for performance is the average *instructions-per-cycle*. This metric is more appropriate than the conventional *total execution-time* metric because the latter allows meaningful comparison only when the size of the problem is constant across different parallelism degrees. Such parallelism model is compatible with the model used by Amdahl's Law [1]. However, a program may adjust the size of the problem according to the execution parameters such as the parallelism degree. Such parallelism model is compatible with Gustafson Law [16]. Indeed some benchmarks in the Parsec benchmark suite adjust the problem size to the parallelism degree. The IPC metric effectively normalizes the performance over the problem size. It should be noted that this assumes the program does not include speculative computation or else the IPC metric does not reflect the performance – an execution with higher degree of parallelism and higher IPC may have larger portion of its speculative computation discarded than an execution with lower degree of parallelism and lower IPC so that the latter completes faster, thus having higher

performance while having lower IPC. The benchmarks in the Parsec benchmark suite do not include speculative computation.

In the Parsec benchmark suite, the degree of parallelism is expressed by the number of *worker-threads*, i.e. the number of threads the program spawns (not all worker-threads necessarily perform computation throughout the program execution, e.g., a thread may block waiting for other threads). The number of worker threads is a runtime parameter of the benchmark. We use simulated architecture that has at least as much cores as there are worker-threads so that core-to-thread allocation does not constitute a parallelism limiting factor.

Table 4-1 summarizes the parameters of the architecture model that is used to study the parallelism parameters.

| Parameter        | Description               |

|------------------|---------------------------|

| N <sub>PE</sub>  | >= #worker-threads        |

| S\$              | 0 (no cache)              |

| N <sub>max</sub> | N <sub>PE</sub>           |

| CPIexe           | 1 [cycles]                |

| tş               | Not applicable (no cache) |

| tm               | 1 [cycles]                |

Table 4-1: Model parameters for the parallelism scalability study

With no algorithmic speculative computation, there are two performance limiting factors (i.e., factors that reduce the IPC):

1. Memory latency

This reduces IPC through incurring extra latency. The degree of IPC reduction depends on the mix of memory and non-memory instructions. This is captured by the workload model parameter  $r_m$ , as described in 2.2.

2. Inter-thread synchronization

This reduces IPC through preventing a thread from executing any instructions while waiting for another thread to complete some computation.

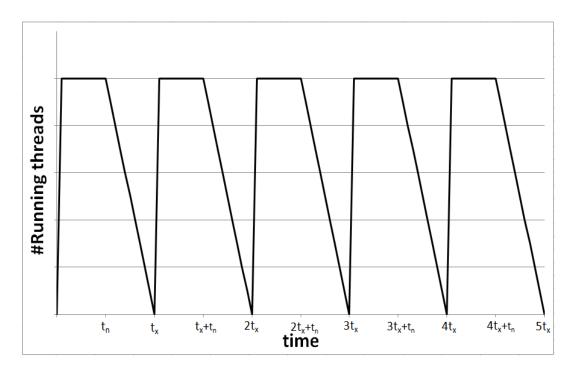

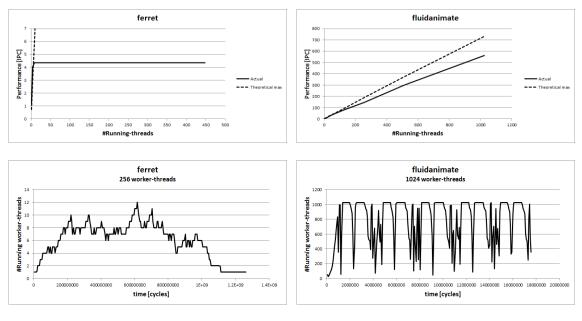

The Inter-thread synchronization reflects the ITC inherent in the workload. Interthread synchronization is known to be a principal performance limiting factor for highly parallel architectures, from GPUs to super-computers. The effect of inter-thread synchronization can be visualized through graph of the number of *running threads* (as opposed to blocked threads) over time. For example, suppose a parallel algorithm involves each thread performing multiple iterations where the iterations of different threads need to execute in lock-step. This requires that at the end of every iteration all threads wait until all other threads complete the respective iteration. This type of synchronization is typically achieved using a Barrier synchronization object [17]. Further suppose that the time it takes a thread to execute an iteration is distributes uniformly between  $t_n$  and  $t_x$ . The number of active threads over time for this algorithm is depicted in **Figure 4-1**. From the beginning of an iteration  $t_0$  until  $t_0+t_n$  the number of active thread is equal to the number of worker threads and from there until  $t_0+t_x$  the number decrease linearly down to 1 (the last one to complete the iteration), at which time the next iteration can start and all the waiting threads are unblocked.

Figure 4-1: thread-context occupancy illustration

For a given number of worker-threads and in the absence of speculative computation, maximum performance is achieved when all the threads are running throughout the program execution. The performance in this case is provided by formula (2-5) in the analytical model (section 2.2). The fact that the architecture that is used to study the parallelism scalability has no cache is equivalent to  $P_{miss}(S_{s,n})=1$ . Therefore, the performance formula (2-5) becomes:

(4-1) **Performance**<sub>max</sub>(n)[IPC] =

$$\frac{n}{CPI_{exe}+r_m \cdot t_m}$$

*n* is the number of worker-threads;  $CPI_{exe}$  and  $t_m$  are described in Table 4-1;  $r_m$  is extracted from the simulation.

A workload is said to have *perfect parallelism scalability* over a range of worker-threads count when its actual performance is equal to the maximum performance as depicted in (4-1) over that range. Such a workload can fully utilize as much parallelism in the range as available in underlying architecture.

In our study we show the actual performance vs. the number of worker-threads of the actual and maximum performance of the various benchmarks in the Parsec benchmark suite. For the ones that do not exhibit perfect parallelism scalability, i.e., limited by inter-

thread synchronization, we show the inter-thread synchronization effects using the graph of running threads over time for several worker-threads counts.

# 4.2. Measurement methodology

Using the simulator described in Chapter 3, we obtain the total number of executed instructions and the total execution time (in cycles) and calculate the IPC. The details of the simulation environment are provided in Appendix: simulation environment.

We measure with the benchmarks running with up to 1984 worker-threads. The upper limit is derived from a limitation of the Pin binary instrumentation framework, which supports programs with up to 2048 threads. Since most of the benchmarks have a control thread in addition to the worker-threads, these benchmarks cannot be instantiated with 2048 worker-threads under Pin. 1984 was chosen because the higher worker-threads count were selected to be multiple of 64 and 1984 is the largest multiple of 64 that is smaller than 2048. To have measurements in reasonable resolution, the worker-threads counts are not spaced evenly across the range. They are spaced more closely in the lower range. So the simulated worker-threads counts are 4-64 in 4 threads interval, 64-128 in 16 threads interval and 128-1984 in 64 threads interval.

Some benchmarks have constraints on the number of worker-threads, such as it must be a power of two. Some do not run properly with order of hundreds and thousands workerthreads. Some spawn multiple threads per worker-thread count so they hit the 2048 threads limit of the Pin binary instrumentation framework with a lower number of worker-threads parameter. We indicate this in the results of the specific benchmark.

The simulations are performed with the "simmedium" data-set unless otherwise indicated in the results of the specific benchmark.

The benchmarks of the Parsec benchmark suite include setup and cleanup steps that are not part of the parallel algorithm, e.g., reading input data from disk to memory, printing summary information etc. To allow excluding these operation from the measurement, the Parsec benchmark suites define *Region of Interest* (ROI), which is the part of the execution that performs the actual parallel algorithm. The ROI start and end are signaled by calls to specific functions. These signals are made available inside the simulator by sensing these calls. To enable this ROI detection by the simulator, the simulator takes the names of the ROI start/end functions as parameters. The ROI start/end notifications inside the simulator are used to reset/sample the simulator's internal performance counters (on ROI begin/end, respectively) so that the startup and cleanup operations are excluded from the simulation statistics.

The benchmarks in the Parsec benchmark suite notify the ROI start just before spawning the worker threads, after preparing the input data-set in memory. However, this means that the thread spawning operation is included in the ROI but this is not really part of the parallel algorithm. Spawning a thread involves some computation that executes in the context of the spawning thread and some thread-startup computation that executes in the context of the newly spawned thread. We'll refer to these as C<sub>prepare</sub> and C<sub>startup</sub>, respectively. While C<sub>startup</sub> of different worker threads can execute in parallel because they execute in the context of different threads, C<sub>prepare</sub> of different worker threads all execute in the context of the spawning thread and hence are serialized. Thus, spawning the worker threads incurs a serial-execution component that is proportional to the number of worker threads; hence its effect increases with the degree of parallelism. To exclude C<sub>prepare</sub> and C<sub>startup</sub> from the ROI, our simulator supports an alternate ROI detection mode, different than detecting the calls to the ROI start/end functions. In this mode the ROI begin is implied from all the threads reaching the thread-entry point function, i.e., after all C<sub>prepare</sub> and C<sub>startup</sub> computations have finished. For this mechanism the simulator takes 2 parameters: a list of thread entry-point functions<sup>4</sup> and the expected number of threads to enter these functions. To ensure all the parallel computation is included in the ROI, the simulator freezes the threads as they reach the thread-entry function so that they do not execute code until all worker-threads have been spawned and reached the thread entry-function (i.e., after  $C_{startup}$ ). This has the effect of a barrier at the beginning of the thread-entry functions. Indeed some benchmarks have explicit barrier in the beginning of their thread-entry function to achieve exactly that. However, the Simulator's effective barrier has the

<sup>&</sup>lt;sup>4</sup> some benchmarks have several entry functions, for different types of worker-threads

advantage that it takes zero simulation time to unblock all the threads, as opposed to a barrier in the benchmark itself, which does consumes simulation execution cycles while actually not being part of the parallel algorithm. Therefore, for the purpose of our simulations we removed barriers in the beginning of thread-entry functions. We indicate this in the results of the specific benchmarks.

Complementary to notifying ROI start just before spawning the worker threads, the benchmarks in the Parsec benchmark suite notify ROI end just after all the worker threads terminate, traditionally referred to as *join*-ing the thread handles. Similar to the case of spawning a thread, joining a thread involves thread-cleanup computations that execute in the context of the joined threads, and computations that execute in the contexts of the joining thread. We'll call them Cterminate, and Cjoin, respectively. While Cterminate of different threads can run in parallel, the C<sub>join</sub> of different threads are serialized in the joining thread. Moreover, worker threads are not necessarily symmetrical with regards to execution time, i.e., some threads may exit sooner than others. This means that the degree of parallelism is reduced towards the end of execution. Like serial execution computation segments, the effect of this "reduced parallelism tail" increases with the increase in the degree of parallelism so we would like to exclude it from the simulation too. This is achieved by the simulator sensing the exit from the thread entry-point functions and using the first exit as the ROI end indicator. This excludes the C<sub>terminate</sub> and C<sub>join</sub> of all threads from ROI, as well as the "reduced parallelism tail". While we recognize that theoretically the "reduced parallelism tail" can be a principal performance bottleneck of a parallel workload<sup>5</sup>, we assume that even if it is, this is not inherent to the parallel algorithm but rather a consequence of the particular implementation. Under this assumption, the tail is not representative of the benchmark's inherent parallelism so excluding it for the purpose of studying the parallel part is desirable.

<sup>&</sup>lt;sup>5</sup> Reference to map-reduce handling of "reduced parallelism tail".

# 4.3. Simulation results

### 4.3.1. blackscholes

The **blackscholes** benchmark contains a barrier at the beginning of the worker-threads in order to maximize parallelism by making all the threads start only after all have been created and reached the starting point. As described in section 4.2, a barrier in the workload itself introduces a serial phase so for our measurements we removed the barrier from the benchmark and replaced it by the simulator's support for worker-threads start synchronization.

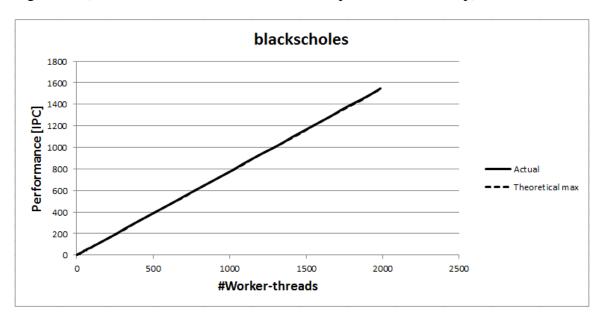

The **blackscholes** benchmark exhibits perfect parallelism scalability, as shown in Figure 4-2 (the curves of the maximum and actual performance overlap).

Figure 4-2: Parallelism scalability - blackscholes

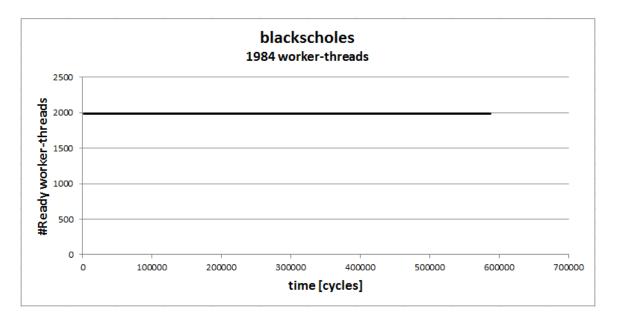

The **blackscholes** benchmark is *embarrassingly parallel*, i.e., there is an abundance of the parallel units of work and they are completely independent – the data-set is partitioned evenly between the worker-threads, which operate on them independently, i.e., with no inter-thread synchronization. This is seen in Figure 4-3, which shows that all worker threads are running throughout the benchmark execution, i.e., they never block to synchronize with other threads (we use the 1948 worker-threads execution as a representative – it is the same with smaller number of worker-threads):

Figure 4-3: Running threads over time - blackscholes

## 4.3.2. bodytrack

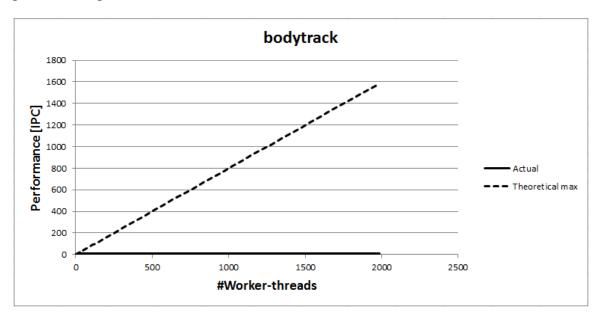

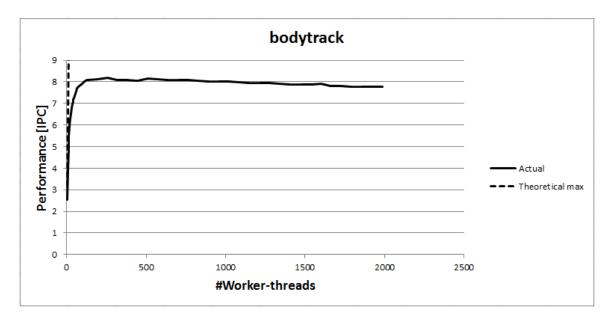

The performance of the **bodytrack** benchmark is shown in Figure 4-4. Figure 4-5 is similar to Figure 4-4 except that the vertical axis is scaled, to provide a more detailed view of the actual performance curve. It shows good scalability up to ~32 threads and the performance plateaus at ~128 worker-threads.

Figure 4-4: Parallelism scalability – bodytrack

Figure 4-5: Parallelism scalability – bodytrack (scaled)

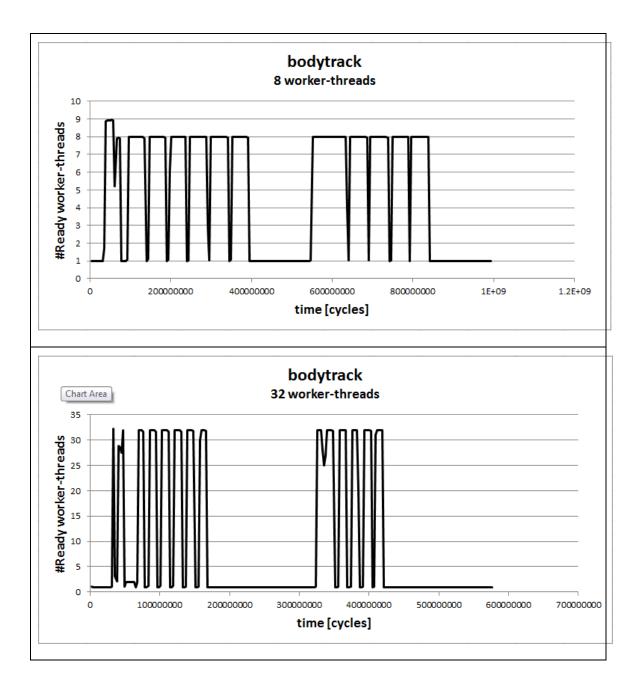

The **bodytrack** benchmark has poor scalability and the running threads over time curves in Figure 4-6 provides the explanation: there is a serial component that is  $\sim 53 \cdot 10^7$  cycles long that increasingly dominates the execution time as the number of worker threads increases.

Figure 4-6: Running threads over time - bodytrack

## 4.3.3. canneal

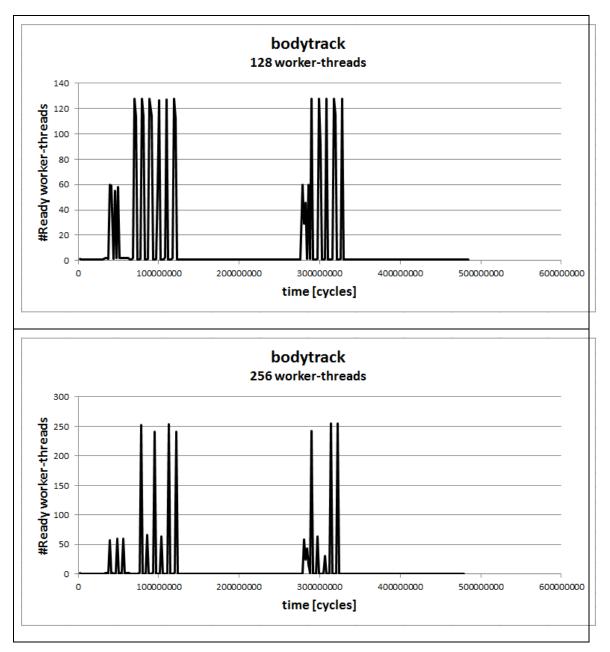

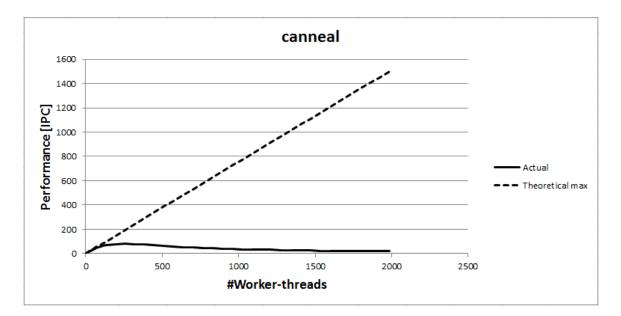

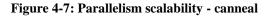

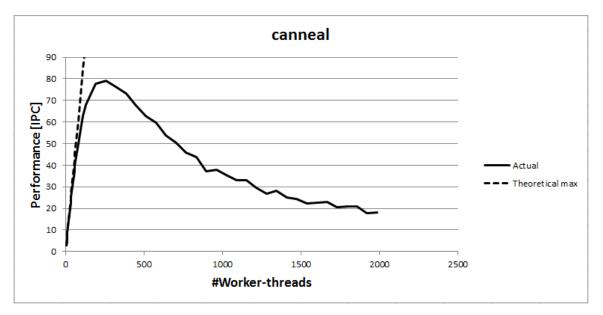

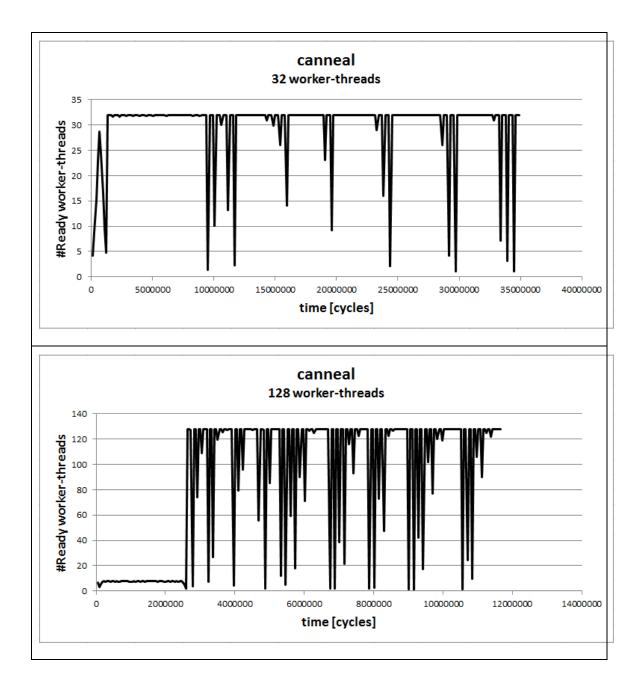

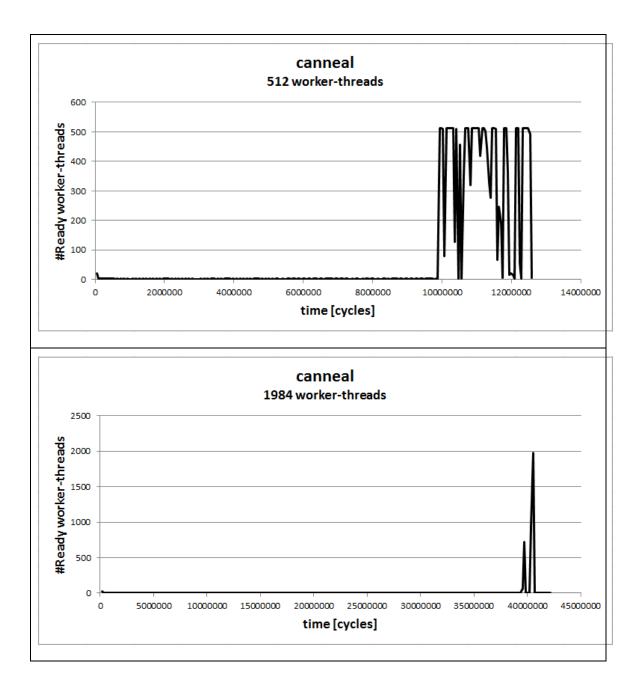

The performance of the **canneal** benchmark is shown in Figure 4-7. Figure 4-8 is similar to Figure 4-7 except that the vertical axis is scaled, to provide a more detailed view of the actual performance curve. It shows that this benchmark has good scalability up to ~128 worker-threads and peak performance at ~256 threads. Beyond that the performance not only doesn't increase, it decreases.

Figure 4-8: Parallelism scalability – canneal (scaled)